# **PSAS** Avionics System Design Project

Michael Kennan Matt McFadden

# **PSAS** Avionics System Design Project

Spring 1999

Revision 3.1

Michael Kennan Matt McFadden

Faculty Advisor: Industry Advisor: Dr. Lee Casperson Andrew Greenberg

## Acknowledgements

This project is presented in partial fulfillment of the authors Senior Project requirements for the Electrical and Computer Engineering Department at Portland State University. We would like to thank our Faculty Advisor Dr. Lee Casperson and our Industry Advisor Andrew Greenberg for their assistance, guidance, and support throughout the course of the project.

# Abstract

To meet the goal of developing an Inertial Navigation System for future rocket flights, the Portland State Aerospace Society (PSAS) requires a testbed system for developing, characterizing, and qualifying sensor and control packages. The system is required to be scalable and modular while meeting weight constraints and environmental standards such as force and temperature tolerance.

This document provides an overview of previous amateur rocketry research performed by the PSAS and describes the authors' design of a robust, scalable, and evolvable rocket avionics architecture. Emphasis is made on modularity, redundancy of critical hardware and software mechanisms, testability, and the maintenance of an open architecture to accommodate future changes to the system.

This is a living document that represents a work in progress. Revisions will continue to be made throughout the development of the LV2 rocket project.

# Table of Contents

| ACKNOWLEDGEMENTS                              | 1 |

|-----------------------------------------------|---|

| ABSTRACT                                      | 2 |

| TABLE OF CONTENTS                             |   |

| TABLE OF FIGURES                              | 5 |

| REVISIONS                                     | 6 |

| INTRODUCTION                                  | 7 |

| BACKGROUND                                    | 8 |

| AESS/PSAS                                     |   |

| LAUNCH VEHICLE ZERO (LV0)                     |   |

| LAUNCH VEHICLE ONE (LV1)                      |   |

| LAUNCH VEHICLE TWO (LV2)                      |   |

| PROBLEM STATEMENT                             |   |

|                                               |   |

| CONSTRAINTS                                   |   |

| DESIGN REQUIREMENTS                           |   |

| OVERALL                                       |   |

| Sensors:                                      |   |

| Proprioceptive sensors                        |   |

| External sensors                              |   |

| COMMUNICATIONS:                               |   |

| Uplink                                        |   |

| Downlink                                      |   |

| Communications subsystem                      |   |

| DATA STORAGE:                                 |   |

| FLIGHT COMPUTER:                              |   |

| ARCHITECTURAL CONSIDERATIONS                  |   |

| CENTRAL/MONOLITHIC ARCHITECTURE               |   |

| SERIAL ARCHITECTURE (DIRECT)                  |   |

| SERIAL ARCHITECTURE (ARBITRATED)              |   |

| DISTRIBUTED ARCHITECTURE                      |   |

| MODULAR ARCHITECTURE                          |   |

| SERIAL ARCHITECTURE WITH HARDWARE ARBITRATION |   |

| IMPLEMENTATION                                |   |

| CANBUS OVERVIEW                               |   |

| How does CAN work?                            |   |

| Identifiers                                   |   |

| Addressing and Arbitration                    |   |

| Error-Checking                                |   |

| Realization                                   |   |

| MODULE OVERVIEW                               |   |

| FLIGHT COMPUTER (FC)            |  |

|---------------------------------|--|

| Hardware                        |  |

| Messaging                       |  |

| Software                        |  |

| COMMUNICATION COMPUTER (CC)     |  |

| Hardware                        |  |

| Messaging                       |  |

| Software                        |  |

| INERTIAL MEASUREMENT UNIT (IMU) |  |

| Hardware                        |  |

| Messaging                       |  |

| Software                        |  |

| DATA ACQUISITION MODULE (DAQ)   |  |

| Hardware                        |  |

| Messaging                       |  |

| Software                        |  |

| FLIGHT RECORDER (FR)            |  |

| Hardware                        |  |

| Messaging                       |  |

| Software                        |  |

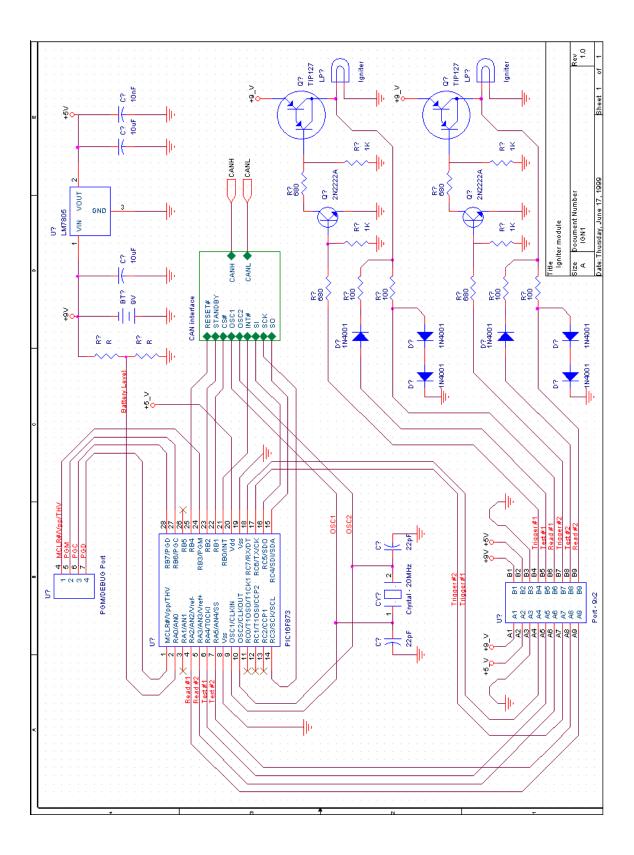

| IGNITERS                        |  |

| Hardware                        |  |

| Messaging                       |  |

| Software                        |  |

| OPERATIONS                      |  |

| Messages                        |  |

| Modes                           |  |

| GROUND SUPPORT                  |  |

| LANS FOR THE FUTURE             |  |

| APPENDIX A: SYSTEM SCHEMATICS   |  |

| PPENDIX B: MESSAGE IDENTIFIERS  |  |

| PPENDIX C: REFERENCES           |  |

# Table of Figures

| Figure 2:    Launch Vehicle Zero (LV0) payload block diagram    10      Figure 3:    Launch Vehicle Zero (LV0) altimeter data    11      Figure 4:    Launch Vehicle Zero (LV1) payload block diagram    13      Figure 5:    Launch Vehicle Zero (LV1) payload block diagram    13      Figure 7:    Figure 7:    Launch Vehicle Zero (LV1) payload block diagram    13      Figure 7:    Figure 7:    Figure 7:    14      Figure 8:    LV1 Z-axis acceleration data    17      Figure 9:    Velocity profile for LV1    19      Figure 11:    Possible Configuration of LV2    22      Figure 12:    Possible Configuration of LV2    20      Figure 13:    Monolithic architecture block diagram    29      Figure 14:    Serial ring architecture block diagram    30      Figure 15:    Distributed architecture block diagram    31      Figure 17:    Modular architecture block diagram    32      Figure 18:    CANbus architecture block diagram    32      Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Connecting to the A/D converter    57      Figure 22:    Con                                | Figure 1:  | Launch Vehicle Zero (LV0)                       | 9  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------|----|

| Figure 3:    Launch Vehicle Zero (LV0) altimeter data    11      Figure 4:    Launch Vehicle Zero (LV1) payload block diagram    12      Figure 5:    Additional specification details for LV1    14      Figure 6:    Additional specification details for LV1    14      Figure 7:    Flight profile for LV1    19      Figure 8:    LV1 Z-axis acceleration data    17      Figure 10:    Position profile for LV1    19      Figure 11:    Pressure sensor altitude profile for LV1    20      Figure 12:    Possible Configuration of LV2    22      Figure 13:    Monolithic architecture block diagram    27      Figure 14:    Serial ring architecture block diagram    28      Figure 15:    Detail of arbitrated serial bus    29      Figure 16:    Distributed architecture block diagram    30      Figure 17:    Modular architecture block diagram    31      Figure 18:    CANbus architecture block diagram    32      Figure 19:    Example of arbitration/prioritization scheme    35      Figure 21:    Frequency-Phase characteristic    55      Figure 22:    Connecting to the A/D converter    57                            | •          | Launch Vehicle Zero (LV0) payload block diagram | 10 |

| Figure 4:    Launch Vehicle One (LV1)    12      Figure 5:    Launch Vehicle Zero (LV1) payload block diagram    13      Figure 6:    Additional specification details for LV1    14      Figure 7:    Flight profile for LV1    17      Figure 8:    LV1 Z-axis acceleration data    17      Figure 9:    Velocity profile for LV1    19      Figure 10:    Position profile for LV1    19      Figure 11:    Pressure sensor altitude profile for LV1    20      Figure 13:    Monolithic architecture block diagram    27      Figure 14:    Serial ring architecture block diagram    28      Figure 15:    Detail of architecture block diagram    30      Figure 16:    Distributed architecture block diagram    30      Figure 17:    Modular architecture block diagram    31      Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Connecting to the A/D converter    57      Figure 22:    Connecting to the A/D converter    57      Figure 23:    Integration approximation in the IMU    59      Figure 24:    Preperature Sensor Schematic    61 <t< td=""><td>Figure 3:</td><td></td><td></td></t<> | Figure 3:  |                                                 |    |

| Figure 5:    Launch Vehicle Zero (LVI) payload block diagram    13      Figure 6:    Additional specification details for LV1    14      Figure 7:    Flight profile for LV1    15      Figure 8:    LVI Z-axis acceleration data    17      Figure 9:    Velocity profile for LV1    19      Figure 11:    Pressure sensor altitude profile for LV1    20      Figure 12:    Possible Configuration of LV2    22      Figure 13:    Monolithic architecture block diagram    27      Figure 14:    Serial ring architecture block diagram    28      Figure 15:    Detail of arbitrated serial bus    29      Figure 16:    Distributed architecture block diagram    30      Figure 17:    Modular architecture block diagram    31      Figure 18:    CANbus architecture block diagram    32      Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Frequency-Phase characteristic    56      Figure 22:    Connecting to the A/D converter    57      Figure 23:    Internal structure of linear accelerometers    62      Figure 24:    Power Monitoring Circuit    61   <                                     | Figure 4:  |                                                 |    |

| Figure 7:    Flight profile for LV1    15      Figure 8:    LV1 Z-axis acceleration data    17      Figure 9:    Velocity profile for LV1    19      Figure 10:    Position profile for LV1    19      Figure 11:    Pressure sensor altitude profile for LV1    20      Figure 12:    Possible Configuration of LV2    22      Figure 13:    Monolithic architecture block diagram    27      Figure 14:    Serial ring architecture block diagram    28      Figure 15:    Detail of architecture block diagram    30      Figure 17:    Modular architecture block diagram    31      Figure 18:    CANbus architecture block diagram    32      Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Frequency-Phase characteristic    56      Figure 22:    Connecting to the A/D converter    57      Figure 23:    Integration approximation in the IMU    59      Figure 24:    Power Monitoring Circuit    61      Figure 25:    Separation Schematic    62      Figure 26:    Temperature Sensor Schematic    57      Figure 31:    Initializatio                                                             | Figure 5:  | Launch Vehicle Zero (LV1) payload block diagram | 13 |

| Figure 7:    Flight profile for LV1    15      Figure 8:    LV1 Z-axis acceleration data    17      Figure 9:    Velocity profile for LV1    19      Figure 10:    Position profile for LV1    19      Figure 11:    Pressure sensor altitude profile for LV1    20      Figure 12:    Possible Configuration of LV2    22      Figure 13:    Monolithic architecture block diagram    27      Figure 14:    Serial ring architecture block diagram    28      Figure 15:    Detail of architecture block diagram    30      Figure 17:    Modular architecture block diagram    31      Figure 18:    CANbus architecture block diagram    32      Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Frequency-Phase characteristic    56      Figure 22:    Connecting to the A/D converter    57      Figure 23:    Integration approximation in the IMU    59      Figure 24:    Power Monitoring Circuit    61      Figure 25:    Separation Schematic    62      Figure 26:    Temperature Sensor Schematic    57      Figure 31:    Initializatio                                                             | Figure 6:  | Additional specification details for LV1        | 14 |

| Figure 8:    LVI Z-axis acceleration data    17      Figure 9:    Velocity profile for LV1    19      Figure 11:    Pressure sensor altitude profile for LV1    20      Figure 12:    Possible Configuration of LV2    22      Figure 13:    Monolithic architecture block diagram    27      Figure 14:    Serial ring architecture block diagram    28      Figure 15:    Detail of arbitrated serial bus    29      Figure 16:    Distributed architecture block diagram    30      Figure 17:    Modular architecture block diagram    32      Figure 18:    CANbus architecture block diagram    32      Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Frequency-Phase characteristic    56      Figure 22:    Connecting to the A/D converter    57      Figure 23:    Integration approximation in the IMU    59      Figure 24:    Power Monitoring Circuit    61      Figure 25:    Separation Sensor Schematic    62      Figure 26:    Temperature Sensor Schematic    62      Figure 27:    Pressure Sensor Schematic    62      Figure 31:                                                          | Figure 7:  |                                                 |    |

| Figure 9:    Velocity profile for LV1    19      Figure 10:    Possition profile for LV1    19      Figure 11:    Pressure sensor altitude profile for LV1    20      Figure 12:    Possible Configuration of LV2    22      Figure 13:    Monolithic architecture block diagram    27      Figure 14:    Serial ring architecture block diagram    29      Figure 15:    Detail of arbitrated serial bus    30      Figure 16:    Distributed architecture block diagram    30      Figure 17:    Modular architecture block diagram    30      Figure 18:    CANbus architecture block diagram    32      Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Frequency-Phase characteristic    56      Figure 22:    Connecting to the A/D converter    57      Figure 23:    Internation approximation in the IMU    59      Figure 24:    Power Monitoring Circuit    61      Figure 25:    Separation Sensor Schematic    62      Figure 26:    Temperature Sensor Schematic    57      Figure 31:    Initialization State Flow Diagram    78      Figure 32: <td>Figure 8:</td> <td></td> <td></td>             | Figure 8:  |                                                 |    |

| Figure 10:    Position profile for LV1    19      Figure 11:    Pressure sensor altitude profile for LV1    20      Figure 12:    Possible Configuration of LV2    22      Figure 13:    Monolithic architecture block diagram    27      Figure 14:    Serial ring architecture block diagram    28      Figure 15:    Detail of arbitrated serial bus    29      Figure 17:    Modular architecture block diagram    30      Figure 18:    CANbus architecture block diagram    31      Figure 19:    Example of arbitration/prioritization scheme    35      Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Frequency-Phase characteristic    56      Figure 22:    Connecting to the A/D converter    57      Figure 23:    Integration approximation in the IMU    59      Figure 24:    Power Monitoring Circuit    61      Figure 25:    Separation Sensor Schematic    62      Figure 32:    Programming the Flash RAM    70      Figure 32:    Programming the Flash RAM    70      Figure 32:    Preflight State Flow Diagram    78      Figure 33: <td>Figure 9:</td> <td></td> <td></td>              | Figure 9:  |                                                 |    |

| Figure 11:    Pressure sensor altitude profile for LV1    20      Figure 12:    Possible Configuration of LV2    22      Figure 13:    Monolithic architecture block diagram    27      Figure 14:    Serial ring architecture block diagram    29      Figure 15:    Detail of arbitrated serial bus    29      Figure 16:    Distributed architecture block diagram    30      Figure 17:    Modular architecture block diagram    31      Figure 18:    CANbus architecture block diagram    32      Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Frequency-Phase characteristic    56      Figure 22:    Connecting to the A/D converter    57      Figure 23:    Integration approximation in the IMU    59      Figure 24:    Power Monitoring Circuit    61      Figure 25:    Separation Sensor Schematic    62      Figure 28:    DAQ Flowchart    65      Figure 31:    Initialization State Flow Diagram    78      Figure 32:    Program flow chart for the Flight Recorder    71      Figure 31:    Initialization State Flow Diagram    78      F                                                 | Figure 10: | Position profile for LV1                        | 19 |

| Figure 12:    Possible Configuration of LV2    22      Figure 13:    Monolithic architecture block diagram    27      Figure 14:    Serial ring architecture block diagram    28      Figure 15:    Detail of arbitrated serial bus    29      Figure 16:    Distributed architecture block diagram    30      Figure 17:    Modular architecture block diagram    31      Figure 18:    CANbus architecture block diagram    32      Figure 20:    Internal structure of linear accelerometers    35      Figure 21:    Frequency-Phase characteristic    56      Figure 22:    Connecting to the A/D converter    57      Figure 23:    Integration approximation in the IMU    59      Figure 24:    Power Monitoring Circuit    61      Figure 25:    Separation Sensor Schematic    62      Figure 26:    Temperature Sensor Schematic    63      Figure 31:    Initialization State Flow Diagram    70      Figure 32:    Programming the Flash RAM    70      Figure 31:    Initialization State Flow Diagram    78      Figure 32:    Program flow chart for the Flight Recorder    71      F                                                 | Figure 11: | Pressure sensor altitude profile for LV1        | 20 |

| Figure 13:    Monolithic architecture block diagram    27      Figure 14:    Serial ring architecture block diagram    28      Figure 15:    Detail of arbitrated serial bus    29      Figure 16:    Distributed architecture block diagram    30      Figure 17:    Modular architecture block diagram    31      Figure 18:    CANbus architecture block diagram    32      Figure 19:    Example of arbitration/prioritization scheme    35      Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Frequency-Phase characteristic    56      Figure 22:    Connecting to the A/D converter    57      Figure 23:    Integration approximation in the IMU    59      Figure 24:    Power Monitoring Circuit    61      Figure 25:    Separation Sensor Schematic    62      Figure 27:    Pressure Sensor Schematic    63      Figure 31:    Initialization State Flow Diagram    70      Figure 32:    Palogram flow chart for the Flight Recorder    71      Figure 33:    Launch State Flow Diagram    78      Figure 34:    Flight State Flow Diagram    80                                                   | Figure 12: |                                                 |    |

| Figure 14:    Serial ring architecture block diagram    28      Figure 15:    Detail of arbitrated serial bus    29      Figure 16:    Distributed architecture block diagram    30      Figure 17:    Modular architecture block diagram    31      Figure 18:    CANbus architecture block diagram    32      Figure 19:    Example of arbitration/prioritization scheme    35      Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Frequency-Phase characteristic    56      Figure 22:    Connecting to the AD converter    57      Figure 23:    Integration approximation in the IMU    59      Figure 24:    Power Monitoring Circuit    61      Figure 25:    Separation Sensor Schematic    62      Figure 28:    DAQ Flowchart    63      Figure 31:    Initialization State Flow Diagram    70      Figure 32:    Programflow chart for the Flight Recorder    71      Figure 32:    Preflight State Flow Diagram    79      Figure 32:    Preflight State Flow Diagram    80      Figure 33:    Launch State Flow Diagram    82      Figure 34:                                                        | Figure 13: |                                                 |    |

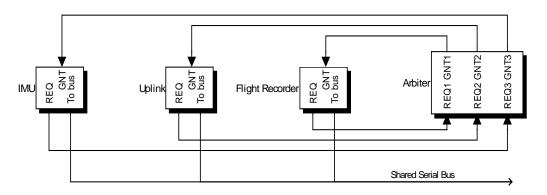

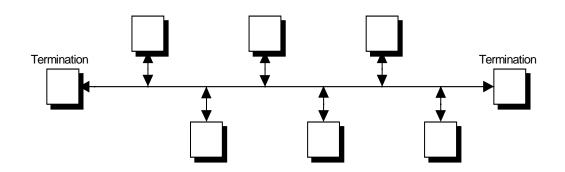

| Figure 15:    Detail of arbitrated serial bus    29      Figure 16:    Distributed architecture block diagram    30      Figure 17:    Modular architecture block diagram    31      Figure 18:    CANbus architecture block diagram    32      Figure 19:    Example of arbitration/prioritization scheme    35      Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Frequency-Phase characteristic    56      Figure 22:    Connecting to the A/D converter    57      Figure 23:    Integration approximation in the IMU    59      Figure 24:    Power Monitoring Circuit    61      Figure 25:    Separation Sensor Schematic    62      Figure 26:    Temperature Sensor Schematic    62      Figure 27:    Pressure Sensor Schematic    63      Figure 30:    Programming the Flash RAM    70      Figure 31:    Initialization State Flow Diagram    78      Figure 32:    Preflight State Flow Diagram    78      Figure 33:    Launch State Flow Diagram    79      Figure 34:    Flight State Flow Diagram    80      Figure 35:    Recover                                                             | Figure 14: |                                                 |    |

| Figure 16:    Distributed architecture block diagram    30      Figure 17:    Modular architecture block diagram    31      Figure 18:    CANbus architecture block diagram    32      Figure 19:    Example of arbitration/prioritization scheme    35      Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Frequency-Phase characteristic    56      Figure 22:    Connecting to the A/D converter    57      Figure 23:    Integration approximation in the IMU    59      Figure 24:    Power Monitoring Circuit    61      Figure 25:    Separation Sensor Schematic    62      Figure 26:    Temperature Sensor Schematic    62      Figure 28:    DAQ Flowchart    65      Figure 29:    Programming the Flash RAM    70      Figure 30:    Programming the Flight Recorder    71      Figure 31:    Initialization State Flow Diagram    78      Figure 32:    Preflight State Flow Diagram    80      Figure 33:    Launch State Flow Diagram    82      Figure 34:    Flight State Flow Diagram    82      Figure 43:    System Overview Sch                                                             | Figure 15: |                                                 |    |

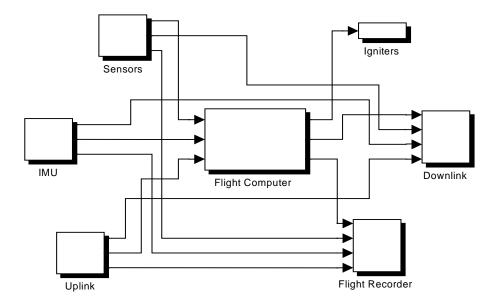

| Figure 17:    Modular architecture block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | Distributed architecture block diagram          | 30 |

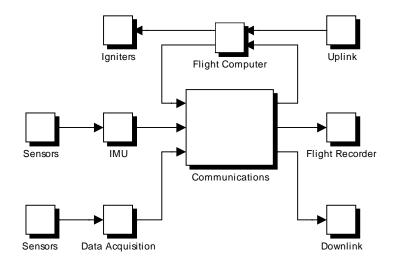

| Figure 18:    CANbus architecture block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 17: |                                                 |    |

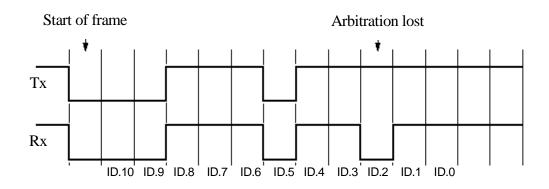

| Figure 19:    Example of arbitration/prioritization scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 18: |                                                 |    |

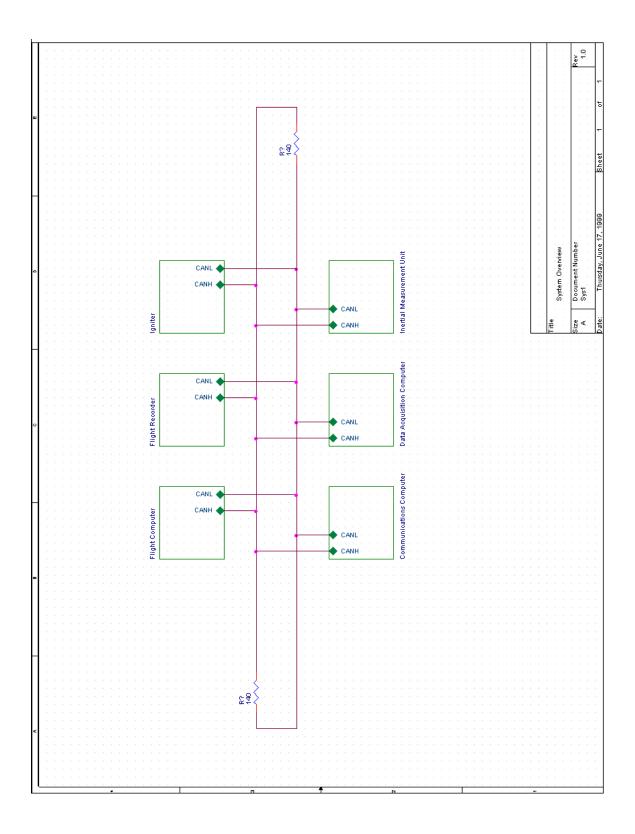

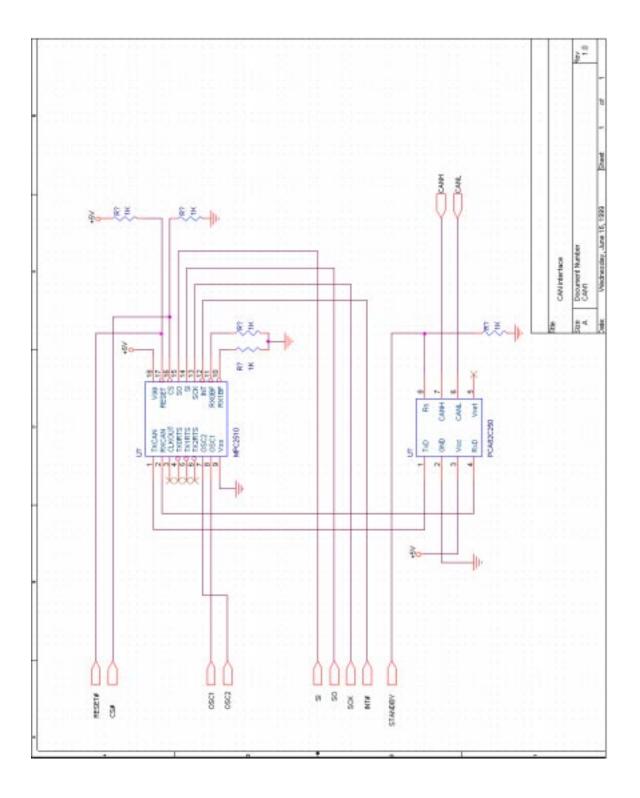

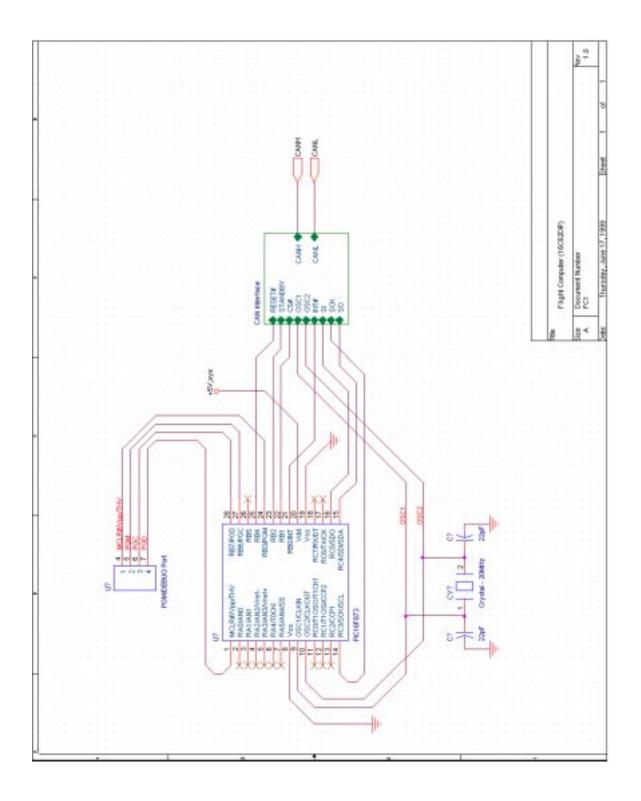

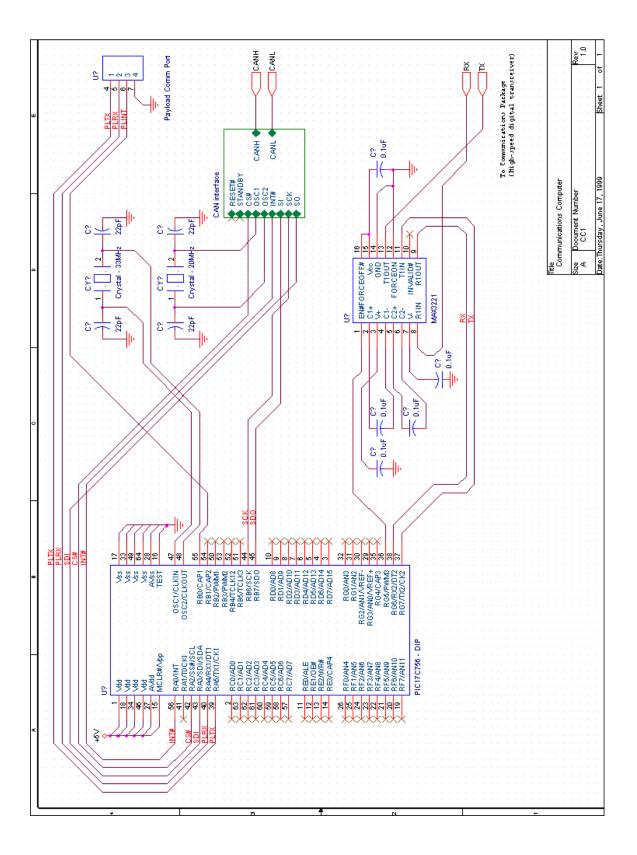

| Figure 20:    Internal structure of linear accelerometers    55      Figure 21:    Frequency-Phase characteristic    56      Figure 22:    Connecting to the A/D converter    57      Figure 23:    Integration approximation in the IMU    59      Figure 24:    Power Monitoring Circuit    61      Figure 25:    Separation Sensor Schematic    61      Figure 26:    Temperature Sensor Schematic    62      Figure 28:    DAQ Flowchart    63      Figure 30:    Programming the Flash RAM    70      Figure 31:    Initialization State Flow Diagram    70      Figure 32:    Preflight State Flow Diagram    79      Figure 33:    Launch State Flow Diagram    79      Figure 34:    Flight State Flow Diagram    80      Figure 35:    Recovery State Flow Diagram    81      Figure 41:    System Overview Schematic    86      Figure A2:    CAN Interface Schematic    87      Figure A3:    Flight Computer Schematic    87      Figure A5:    Inertial Measurement Unit Schematic    89      Figure A5:    Inertial Measurement Unit Schematic    90  <                                                                                 | 0          |                                                 |    |

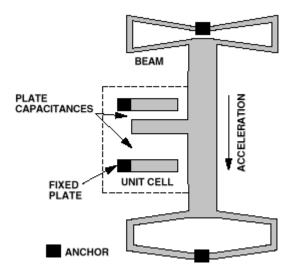

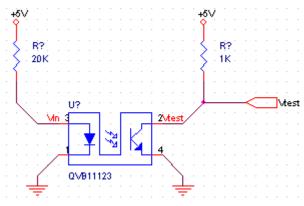

| Figure 21:    Frequency-Phase characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0          | Internal structure of linear accelerometers     | 55 |

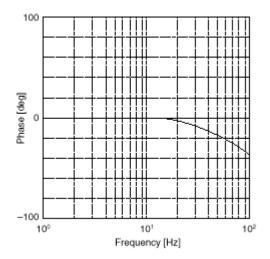

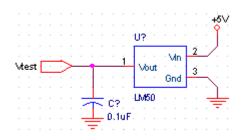

| Figure 22:    Connecting to the A/D converter    57      Figure 23:    Integration approximation in the IMU    59      Figure 24:    Power Monitoring Circuit    61      Figure 25:    Separation Sensor Schematic    61      Figure 26:    Temperature Sensor Schematic    62      Figure 27:    Pressure Sensor Schematic    63      Figure 28:    DAQ Flowchart    65      Figure 29:    Programming the Flash RAM    70      Figure 30:    Program flow chart for the Flight Recorder    71      Figure 31:    Initialization State Flow Diagram    78      Figure 32:    Preflight State Flow Diagram    79      Figure 33:    Launch State Flow Diagram    80      Figure 35:    Recovery State Flow Diagram    81      Figure 35:    Recovery State Flow Diagram    82      Figure A1:    System Overview Schematic    87      Figure A2:    CAN Interface Schematic    87      Figure A3:    Flight Computer Schematic    88      Figure A3:    Flight Computer Schematic    89      Figure A4:    Communication Computer Schematic    90                                                                                                     | Figure 21: |                                                 |    |

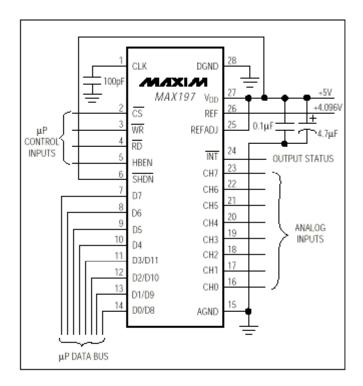

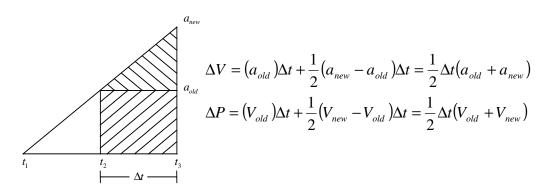

| Figure 23:    Integration approximation in the IMU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0          |                                                 |    |

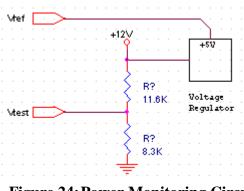

| Figure 24:Power Monitoring Circuit61Figure 25:Separation Sensor Schematic61Figure 26:Temperature Sensor Schematic62Figure 27:Pressure Sensor Schematic63Figure 28:DAQ Flowchart65Figure 29:Programming the Flash RAM70Figure 30:Program flow chart for the Flight Recorder71Figure 31:Initialization State Flow Diagram78Figure 32:Preflight State Flow Diagram79Figure 33:Launch State Flow Diagram80Figure 34:Flight State Flow Diagram81Figure 35:Recovery State Flow Diagram82Figure 41:System Overview Schematic86Figure A2:CAN Interface Schematic87Figure A3:Flight Computer Schematic88Figure A3:Flight Computer Schematic89Figure A5:Inertial Measurement Unit Schematic90Figure A7:Flight Recorder Schematic92Figure A8:Flash RAM Unit Schematic93                                                                                                                                                                                                                                                                                                                                                                                          | Figure 23: |                                                 |    |

| Figure 25:Separation Sensor Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 24: |                                                 |    |

| Figure 26:Temperature Sensor Schematic62Figure 27:Pressure Sensor Schematic63Figure 28:DAQ Flowchart65Figure 29:Programming the Flash RAM70Figure 30:Program flow chart for the Flight Recorder71Figure 31:Initialization State Flow Diagram78Figure 32:Preflight State Flow Diagram79Figure 33:Launch State Flow Diagram80Figure 34:Flight State Flow Diagram81Figure 35:Recovery State Flow Diagram82Figure 41:System Overview Schematic86Figure A3:Flight Computer Schematic87Figure A3:Flight Computer Schematic89Figure A4:Communication Computer Schematic90Figure A5:Inertial Measurement Unit Schematic91Figure A7:Flight Recorder Schematic92Figure A8:Flash RAM Unit Schematic93                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                                                 |    |

| Figure 27:Pressure Sensor Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                                                 |    |

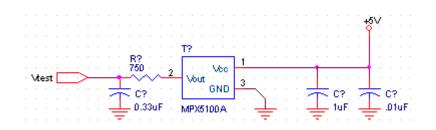

| Figure 28:DAQ Flowchart65Figure 29:Programming the Flash RAM70Figure 30:Program flow chart for the Flight Recorder71Figure 31:Initialization State Flow Diagram78Figure 32:Preflight State Flow Diagram79Figure 33:Launch State Flow Diagram80Figure 34:Flight State Flow Diagram81Figure 35:Recovery State Flow Diagram82Figure A1:System Overview Schematic86Figure A2:CAN Interface Schematic87Figure A3:Flight Computer Schematic88Figure A3:Flight Measurement Unit Schematic89Figure A5:Inertial Measurement Unit Schematic90Figure A7:Flight Recorder Schematic93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 27: |                                                 |    |

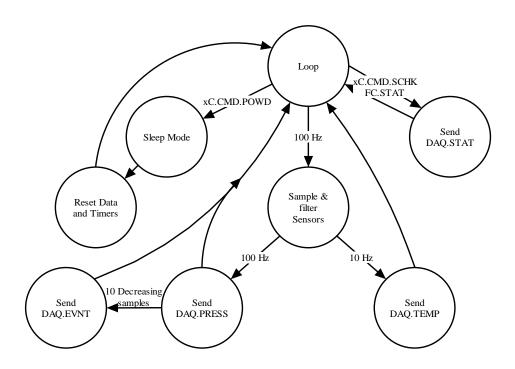

| Figure 29:Programming the Flash RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 28: |                                                 |    |

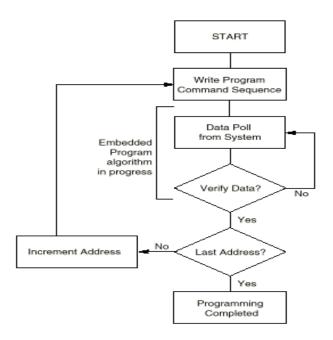

| Figure 30:Program flow chart for the Flight Recorder71Figure 31:Initialization State Flow Diagram78Figure 32:Preflight State Flow Diagram79Figure 33:Launch State Flow Diagram80Figure 34:Flight State Flow Diagram81Figure 35:Recovery State Flow Diagram82Figure 41:System Overview Schematic86Figure A2:CAN Interface Schematic87Figure A3:Flight Computer Schematic88Figure A4:Communication Computer Schematic89Figure A5:Inertial Measurement Unit Schematic90Figure A6:Data Acquisition Module Schematic91Figure A7:Flight Recorder Schematic92Figure A8:Flash RAM Unit Schematic93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                                                 |    |

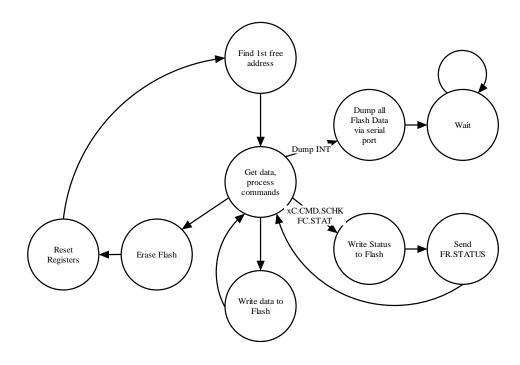

| Figure 31:Initialization State Flow Diagram78Figure 32:Preflight State Flow Diagram79Figure 33:Launch State Flow Diagram80Figure 34:Flight State Flow Diagram81Figure 35:Recovery State Flow Diagram82Figure 35:Recovery State Flow Diagram82Figure A1:System Overview Schematic86Figure A2:CAN Interface Schematic87Figure A3:Flight Computer Schematic88Figure A4:Communication Computer Schematic89Figure A5:Inertial Measurement Unit Schematic90Figure A6:Data Acquisition Module Schematic91Figure A7:Flight Recorder Schematic92Figure A8:Flash RAM Unit Schematic93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0          | Program flow chart for the Flight Recorder      | 71 |

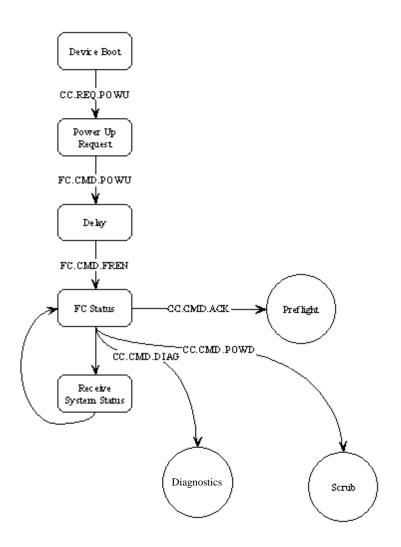

| Figure 32:Preflight State Flow Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0          |                                                 |    |

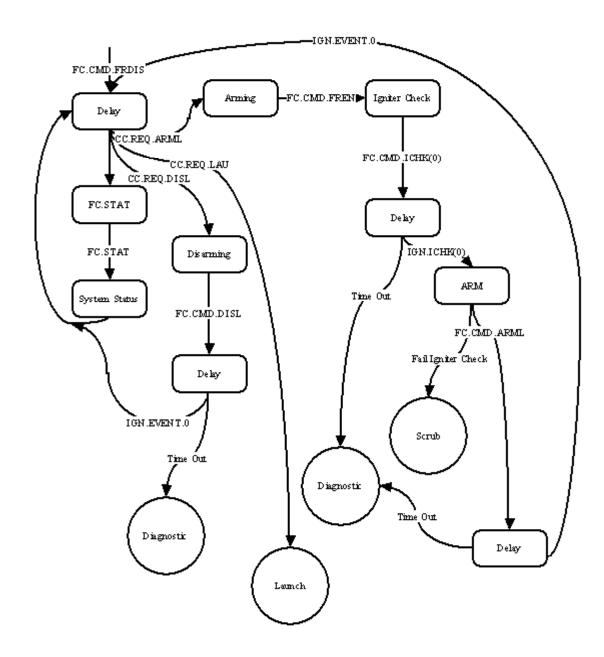

| Figure 33:Launch State Flow Diagram80Figure 34:Flight State Flow Diagram81Figure 35:Recovery State Flow Diagram82Figure A1:System Overview Schematic86Figure A2:CAN Interface Schematic87Figure A3:Flight Computer Schematic88Figure A4:Communication Computer Schematic89Figure A5:Inertial Measurement Unit Schematic90Figure A6:Data Acquisition Module Schematic91Figure A7:Flight Recorder Schematic92Figure A8:Flash RAM Unit Schematic93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |                                                 |    |

| Figure 34:Flight State Flow Diagram81Figure 35:Recovery State Flow Diagram82Figure 35:System Overview Schematic86Figure A1:System Overview Schematic87Figure A2:CAN Interface Schematic87Figure A3:Flight Computer Schematic88Figure A4:Communication Computer Schematic89Figure A5:Inertial Measurement Unit Schematic90Figure A6:Data Acquisition Module Schematic91Figure A7:Flight Recorder Schematic92Figure A8:Flash RAM Unit Schematic93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •          |                                                 |    |

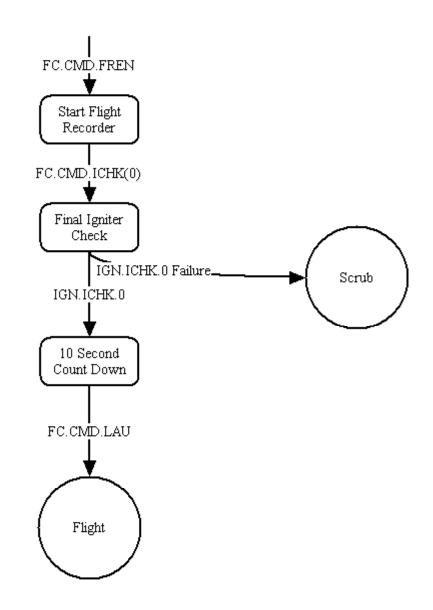

| Figure 35:Recovery State Flow Diagram82Figure A1:System Overview Schematic86Figure A2:CAN Interface Schematic87Figure A3:Flight Computer Schematic88Figure A4:Communication Computer Schematic89Figure A5:Inertial Measurement Unit Schematic90Figure A6:Data Acquisition Module Schematic91Figure A7:Flight Recorder Schematic92Figure A8:Flash RAM Unit Schematic93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0          |                                                 |    |

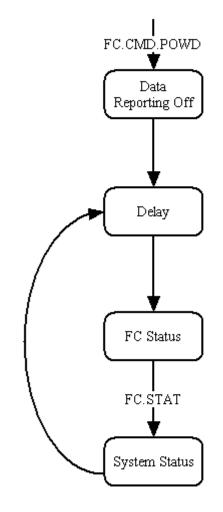

| Figure A1:System Overview Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U U        |                                                 |    |

| Figure A2:CAN Interface Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |                                                 |    |

| Figure A3:Flight Computer Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                                                 |    |

| Figure A4:Communication Computer Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -          |                                                 |    |

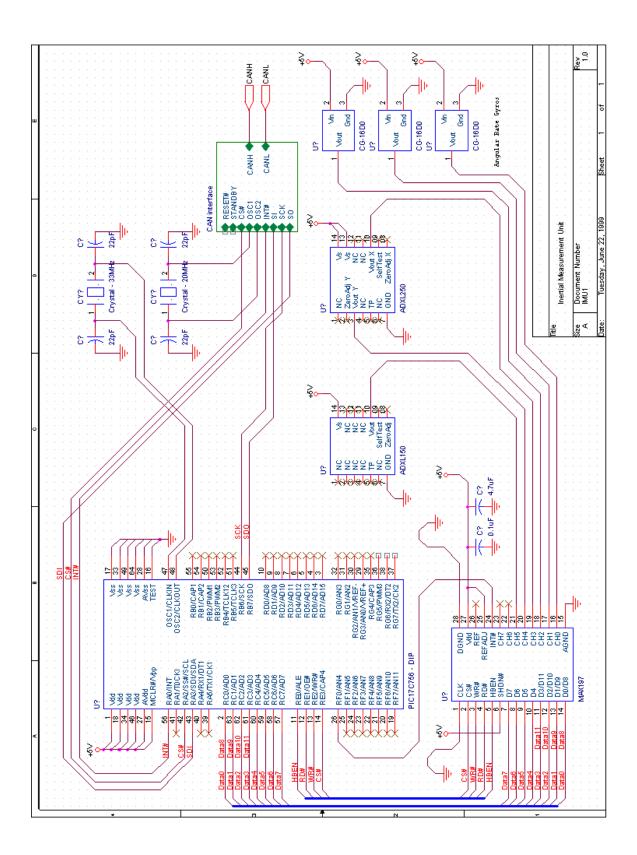

| Figure A5:Inertial Measurement Unit Schematic90Figure A6:Data Acquisition Module Schematic91Figure A7:Flight Recorder Schematic92Figure A8:Flash RAM Unit Schematic93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                                                 |    |

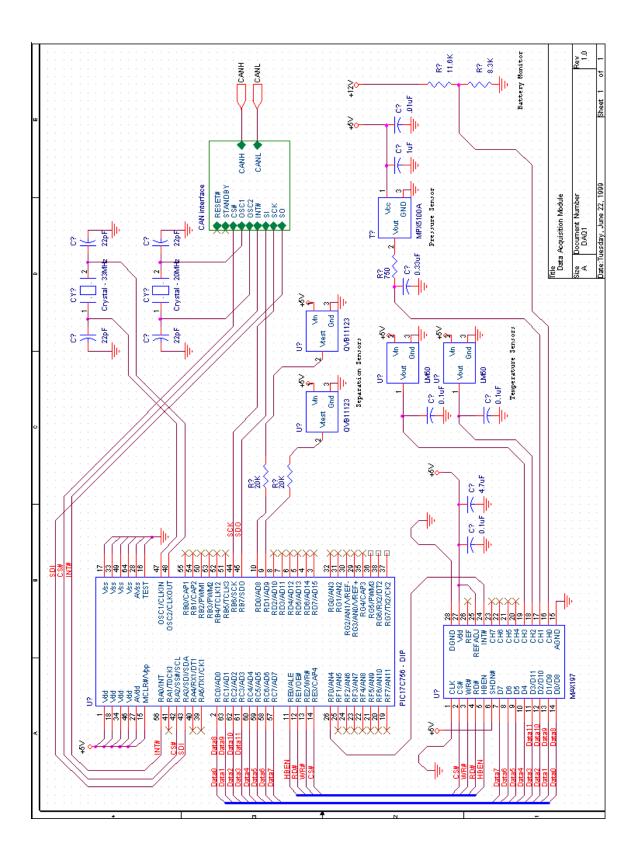

| Figure A6:Data Acquisition Module Schematic91Figure A7:Flight Recorder Schematic92Figure A8:Flash RAM Unit Schematic93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                 |    |

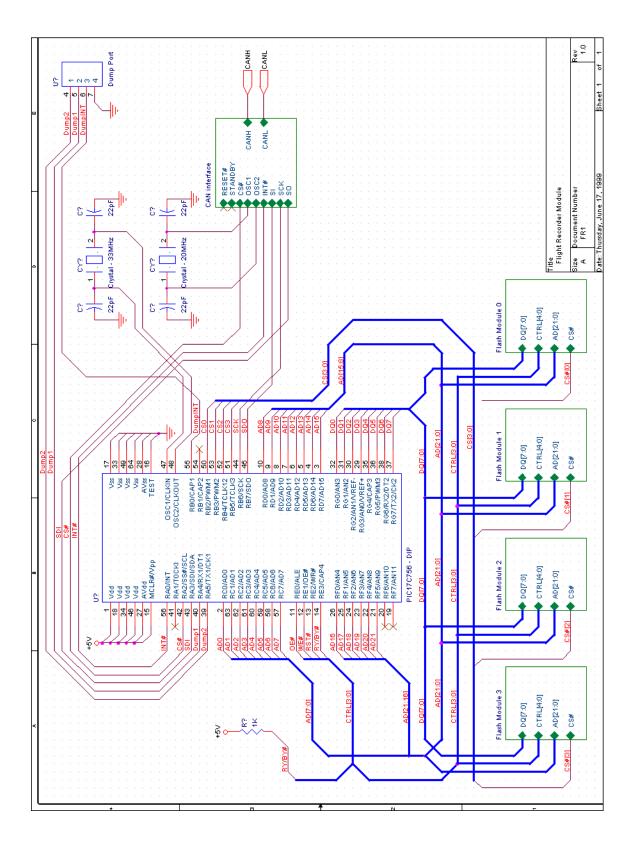

| Figure A7:Flight Recorder Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                                                 |    |

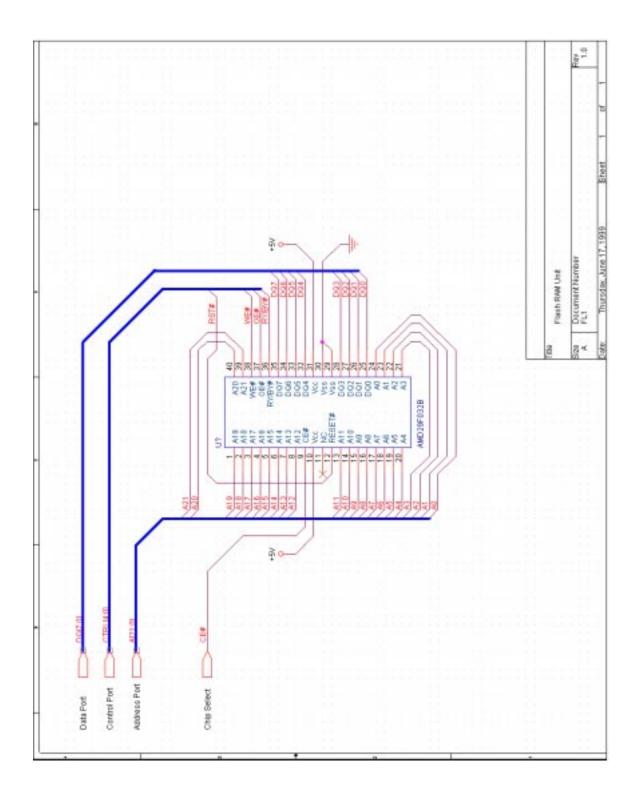

| Figure A8: Flash RAM Unit Schematic93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                                                 |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |                                                 |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0          |                                                 |    |

# Revisions

| Revision Number | vision Number Notes                        |         |

|-----------------|--------------------------------------------|---------|

| 1.0             | Initial Draft Proposal Created             | 1/16/99 |

| 1.1             | First AESS/PSAS submission                 | 2/5/99  |

| 1.2             | Second AESS/PSAS submission                | 2/12/99 |

| 1.3             | First academic submission to Dr. Casperson | 2/18/99 |

| 2.0             | Initial Draft of Design Document Created   | 3/18/99 |

| 3.0             | CANbus implementation, first draft         | 6/1/99  |

| 3.1             | CANbus implementation, final submission    | 6/25/99 |

### Introduction

The Portland State Aerospace Society (PSAS) has been involved in Amateur rocketry developing a microcomputer-controlled intelligent rocket avionics package. The current design has a monolithic architecture specific to the present launch vehicle. To meet future launch vehicle requirements (and as an exercise in many aspects of aerospace systems engineering), we have designed a new avionics system that emphasizes modularity and testability and will aid in the development of an Inertial Navigation System to be used on future flights.

This document will provide an overview of the previous amateur rocketry work by the PSAS, a look at the work that is happening in the present, and an outline of our plans for the future. In the 'Background' section we will discuss prior rocket projects, the state of the art in amateur rocketry today, and our need for a more advanced system. We will then define the problem at hand, discussing the design requirements and constraints that apply to the avionics system design project and examining candidate system architectures. In the 'Implementation' section, we describe our avionics system design and provide an explanation of the architecture we chose to use. In the final section, we will discuss our plans for the future and the direction the PSAS is headed.

# Background

#### AESS/PSAS

The Portland State University (PSU) student chapter of the Aerospace and Electrical Systems Society (AESS) was created in the summer of 1997. The AESS is a technical society of the Institute of Electrical and Electronics Engineers (IEEE), an international professional organization for electrical engineers. The PSU chapter of the AESS was the first student chapter of the society in the United States.

In the Fall of 1998, the Portland State Aerospace Society (PSAS) was formed as a university-recognized student group, allowing anyone from the community (not just AESS/IEEE members) to contribute to the project.

As a group of engineering students and professionals, the PSAS seeks to gain aerospace systems engineering experience and develop "real world" engineering skills by tackling a challenging project.

The ultimate aim of the group is to develop a sophisticated avionics system for highpowered amateur rockets. Many other groups and individuals involved in amateur rocketry are actively advancing "traditional" rocket body and motor design, but it is apparent that few are pursuing the development of any sort of advanced avionics or scientific instrumentation payload.

The original goal of the PSAS was to develop a proof-of-concept vehicle to demonstrate the feasibility of the following:

- broadcasting live video using Amateur Television,

- using the audio channel of the video stream to transmit telemetry data, and

- using inexpensive sensors under microprocessor control to gather scientific data.

This goal was met in June 1998 with the development of Launch Vehicle Zero.

#### Launch Vehicle Zero (LV0)

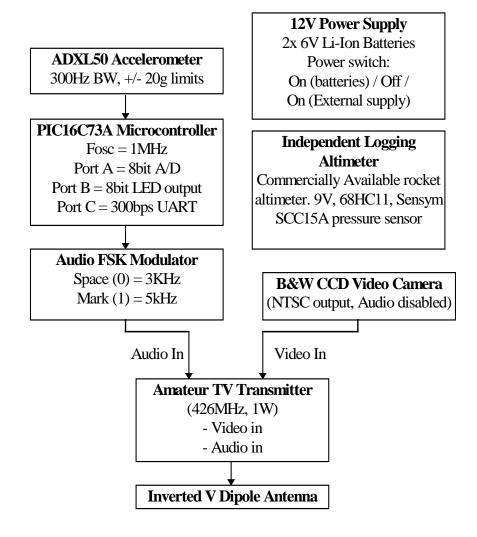

Launch Vehicle Zero (LV0) was the first rocket project developed by the PSAS. LV0's payload module was composed of 3 main systems: The Amateur Television Video (ATV) transmitter system, a vertically aligned (Z-axis) solid-state accelerometer that was fed into a 300 bps digital data down link, and an altimeter.

The rocket-based ATV system was composed of a miniature NTSC black-and-white CCD camera and a transmitter tuned to the 70-cm band allocated for amateur television and radio. The signal from the CCD was fed into the transmitter, which broadcasted at 440 MHz to a ground station equipped with the appropriate antenna and receiver configuration. On the ground, the video signal was viewed real-time and recorded onto videotape.

The Analog Device's ADXL50 solid-state (micro-machined) accelerometer was incorporated in a telemetry package designed to measure the rocket's acceleration profile and transmit the data to the ground station. To accomplish this, the output from the accelerometer was digitized by a PIC16C73A microcontroller and directed to a 300 bps modem. The analog signal from the modem was transmitted to the ground via the audio channel of the ATV signal. On the ground the telemetry data was recorded onto a computer for later analysis.

Also on board the rocket was a commercially available altimeter interfaced with a Motorola 68HC11 microcontroller and a 12-bit A/D converter. All data from the altimeter was stored in battery backed RAM, and retrieved for later analysis.

Specifications for LV0 include:

| Airframe | : | Cardboard with 3 layers fiberglass |

|----------|---|------------------------------------|

| Length   | : | 72 inches                          |

| Weight   | : | 12.2 lbs.                          |

| Motor    | : | 700 Ns solid propellant motor      |

| Recovery | : | Payload - 4-ft parachute           |

|          |   | Body - 3-ft parachute              |

Figure 1: Launch Vehicle Zero (LV0)

LV0 contained no flight-sequencing computer. Separation and recovery were handled by a chemically timed motor ejection charge. The block diagram of the LV0 payload is shown below in Figure 2.

Figure 2: Launch Vehicle Zero (LV0) payload block diagram

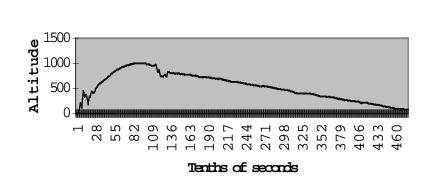

The launch of LV0 occurred on June 7th 1998 in Monroe, Washington. The rocket reached an altitude of 1200 feet, successfully transmitting live video to the ground and internally logging altimeter data throughout the flight. The separation and recovery system worked as predicted, but the digital downlink system failed due to a short in the data transmit line.

The altimeter data from the LV0 flight is shown on the following page.

Figure 3: Launch Vehicle Zero (LV0) altimeter data

From the experience with LV0, the PSAS developed a number of improved design criteria for future launches. These include:

- robust interconnects,

- improved flight control via onboard flight computer, and

- emergency flight control via radio uplink.

Implementation of these criteria in a new rocket design led to the development of Launch Vehicle 1 (LV1).

#### Launch Vehicle One (LV1)

In addition to addressing the issues raised by LV0, the PSAS felt that it was necessary to begin developing basic avionics systems that could grow with future designs, and to include a scientific instrumentation payload for flight profiling and data logging.

Specifications for LV1 include:

| Airframe | : | Carbon fiber body with fiberglass payload |

|----------|---|-------------------------------------------|

| Length   | : | 132 inches                                |

| Weight   | : | 46 lbs.                                   |

| Motor    | : | Up to 10,000 Ns solid propellant motor    |

| Recovery | : | Payload - (3) 3.5 ft parachutes           |

|          |   | Body - 2 stage parachute (drogue/main)    |

Figure 4: Launch Vehicle One (LV1)

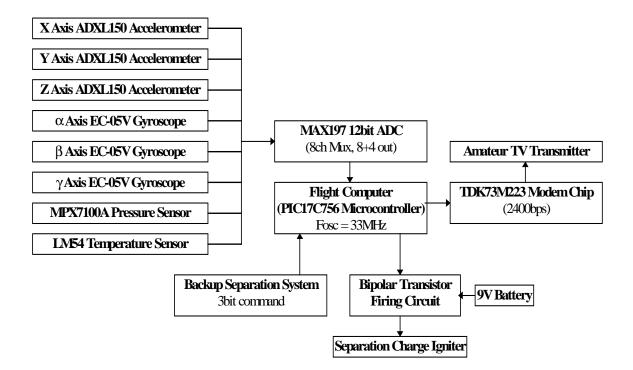

LV1 subsystems include a payload module and an Interface Plate Release System (IPRS).

The payload module includes the following components:

- A color CCD video camera with an ATV transmitter,

- a 2400bps digital data downlink for telemetry data,

- a 2m amateur radio DTMF-activated uplink for manual recovery system control,

- accelerometers and rotational gyro's measuring 3 linear axes and 3 rotational axes,

- pressure and temperature sensors, and

- a flight computer powered by a PIC17C42 microcontroller for flight sequencing.

The accelerometers and rotational gyros form an Inertial Measurement Unit (IMU) with 6 degrees-of-freedom (6-DOF) which will serve as a prototype for the development of a future Inertial Navigation System (INS).

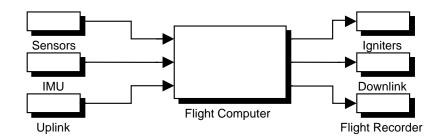

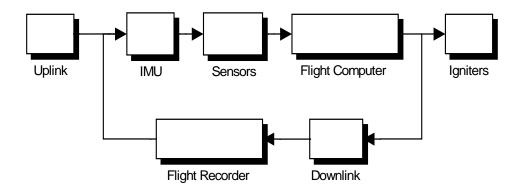

Figure 5: Launch Vehicle Zero (LV1) payload block diagram

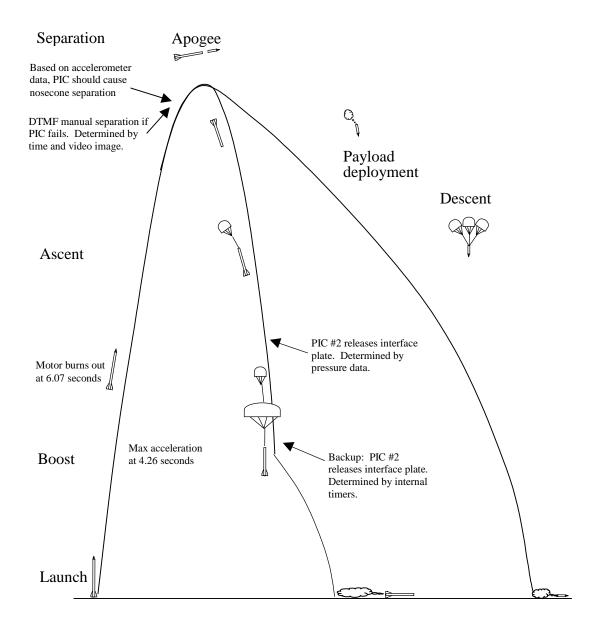

The Interface Plate Release System (IPRS) is responsible for deploying the main rocket body's recovery chutes and is independent of the main payload module. As shown in the flight profile (shown on the next page in Figure 6), the main rocket body falls toward the earth until the pressure sensors or internal timers indicate that it is time to deploy the chutes. Earlier release of the chutes would result in excessive 'hang-time', complicating location and retrieval of the rocket body; later release of the chutes (known as a 'lawn-dart' landing) would simplify location and retrieval of the rocket body but could result in unacceptable damages.

Additional LV1 details are shown in Figure 6, on the next page:

Porland State University AESS/PSAS Launch Vehicle No.1

**Payload Dimensions**

LV-1 Contains 3 payload compartments :

2 primary cylindrical compartments for scientific payloads.

1 secondary conical compartment in the nose section for flight avionics.

The 2 primary compartments will be available for 'ride along' autonomous payload modules. We want to encourage other schools and groups to design and build experiments to fly onboard this and upcoming launch vehicles.

The primary payload compartments will have access to the external environment.

Payload space and launch dates will be variable.

Payload Bay No. 1 (conical) : (reserved for rocket)

ayload Bay No. 2 (cylindrical) : 4.2" dia. aluminum rack w/ fiberglass skin. length is negotiable. 16" maximum

Payload Bay No. 3 (cylindrical) : 3" dia. fixed aluminum rack for slide in modules, carbon fiber skin. 0.25" mounting holes on 1" centers entire length of rail. length is negotiable. 30" maximum.

#### Figure 6: Additional specification details for LV1

The planned flight profile for LV1 is shown below.

Figure 7: Flight profile for LV1

The launch of LV1 occurred on April 11th 1999 at the PSAS launch site near Millikan, Oregon. The rocket reached an altitude of slightly more than 12000 ft, successfully transmitting data and video to the ground support station throughout the flight.

A total of 11,252 Z-axis acceleration data points were received from the rocket throughout the flight, sampled by the MAX197 12-bit A/D converter. Of these, there were approximately 230 obviously erroneous values resulting from bit-flips; 60% of these errors were bit-sets (a false '1' detected) and 40% were bit-clears (a false '0' detected). The errors were corrected by determining whether or not an outlying data point differed from the general trend by the addition or subtraction of a large power of 2 corresponding to one of the 4 most significant bits (MSBs). Obviously it is likely that there were bit-flips in the lower bits as well, but these would be more difficult to detect since the deviation from the general trend would be less noticeable.

If we assume that bit-flip errors can be reliably detected only if they occur in the 4 most significant bits, then only one third of the errors were detected and the total reception error is (3 times the detected error) = 3 \* 230 errors / 11252 total points = 6% error. Future systems must include cyclical redundancy check (CRC), error correction code (ECC), or some other mechanism which is capable of detecting and possible correcting this sort of error.

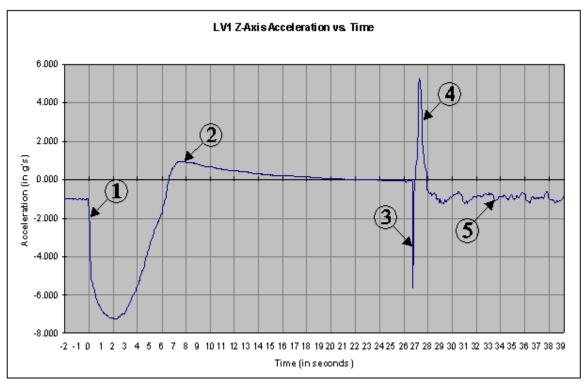

Figure 8 (next page) shows the Z-axis acceleration profile for the flight of LV1. The numbered labels denote interesting portions of the flight; these are discussed below. A note on terminology: all acceleration descriptions are referenced to the ground, i.e. 'negative acceleration' is the result of forces that push the body upwards or create a downward pull on the sensor (such as the rocket motor, the separation charge, and the earth's gravitational field), and 'positive acceleration' is the result of forces that push the body downward (such as wind resistance effects and the opening of the chutes while the rocket was still ascending).

1. Boost phase

Prior to liftoff, the only acceleration experienced by the rocket was a steady 1 'g' downward. At time t = 0s, the motor ignited and the rocket left the launchpad. Maximum acceleration was reached at time t = 2.17s, when the rocket was experiencing 7.27 'g's downward.

2. Ascent phase

As the motor continued to burn through its thrust curve, the diminishing effects of the motor thrust and the increasing effects of air resistance (which is proportional to the cube of the velocity) reduced the acceleration. At t = 6.3s, the air resistance component of the acceleration began to exceed the thrust component and the net acceleration on the avionics system became positive.

Shortly thereafter (at time t = 6.54s) the peak velocity of 596.2mph (0.795 Mach) was reached. As the rocket continued upwards, the effects of the air drag continued to negate the acceleration from the motor, as shown by the asymptotic decay of the graph towards zero.

3. Separation

At time t = 26.75s, the payload/avionics system was forcibly separated from the rocket body by the separation charge, giving the payload a slight boost in upward velocity.

4. Chute Deployment

As the chutes deploy from the rear of the module, the payload experiences a sudden deceleration.

5. Descent

The avionics system floats to the ground. Acceleration oscillates around 1 'g' downward due to the swinging of the avionics system on the three payload chutes. Note that the graph shows only the first 39 seconds of flight- the actual time of flight was 466 seconds.

Figure 8: LV1 Z-axis acceleration data

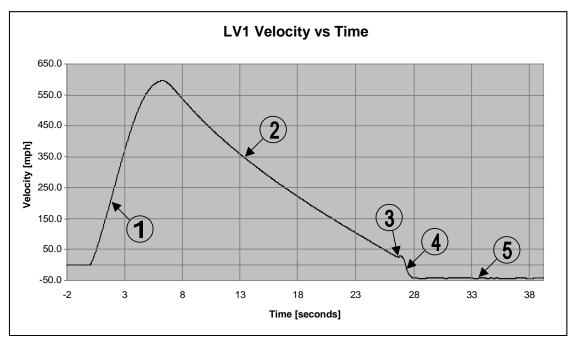

Figure 9 (shown on the next page) shows the Z-axis velocity profile for the flight of LV1. This data was obtained by integrating the acceleration data (disregarding the constant 1'g' acceleration due to gravity). Despite the accumulative errors that result from the integration process, this profile shows the expected behavior:

1. Boost phase

Velocity was initially zero as the rocket sat on the launch pad. At time t = 0s, the motor ignited and the rocket accelerated upwards, rising steadily throughout the boost phase.

2. Ascent phase

At 6.54s, the motor burn is complete and the air resistance exerts its effect on the speed of the rocket throughout the coast phase. The rocket is still continuing upwards as air resistance and gravity erode its momentum.

3. Separation

At 26.75s, the separation charge ignites, giving a slight boost to the velocity of the payload as it is ejected from the main body. Though the rocket still has a non-zero upward velocity, the separation effectively declared this point to be apogee, since the rocket will not continue upwards when the nosecone is absent and the chutes deploy. (The rocket was not in fact going 25 mph at separation as the graph shows. This discrepancy is due to accumulative integration errors).

4. Chute Deployment

As the chutes deploy from the rear of the module, payload velocity decreases to zero and then becomes negative as the payload begins to descend. There is a sudden impulse as the nosecone, which houses the telemetry package, is stopped by the chutes and reverses direction.

5. Descent

The chutes quickly restrict the payload to its terminal velocity.

**Figure 9: Velocity profile for LV1**

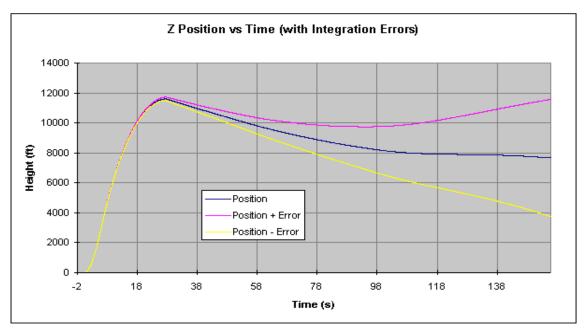

Integrating the acceleration data a second time produces a graph of the position. The accumulated integration errors, however, severely undermine the validity of the graph, as shown in Figure 10 below.

Figure 10: Position profile for LV1

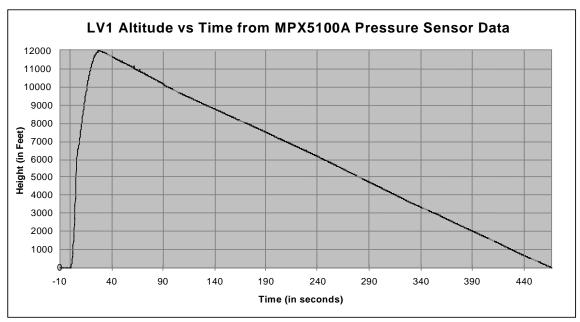

To more accurately determine the height of the rocket, the pressure sensor data was analyzed as shown in Figure 11 below. This data lent itself to a much more meaningful interpretation.

Figure 11: Pressure sensor altitude profile for LV1

As shown in the previous graphs, it may be necessary to combine a number of sources of data to determine the 'correct' telemetry. For an actively guided system, it will be necessary to combine data from the accelerometers and pressure sensors as well as possible Global Positioning System (GPS) data and radio packet time-of-flight indicators. Other possibilities include a sun sensor mounted in the nosecone and high-performance sensors such as ring laser gyros.

With all telemetry measurements it will be necessary to account for signal latency. Time-of-flight, GPS satellite linkup, and even A/D-conversion delays become significant when the rocket is moving at speeds nearing 1 Mach, since by the time a reading has been processed a large distance will have been covered by the rocket. This will necessitate a successive-approximation approach wherein the avionics package will use its current position and heading data to predict where it will be when the next reading occurs; the next reading can then be used to update the approximation and minimize positional error.

#### Launch Vehicle Two (LV2)

To achieve orbit (or very high altitudes) it is necessary to integrate an Inertial Measurement Unit (IMU) with an active guidance system to create an Inertial Navigation System (INS). Prior PSAS rockets have taken steps to develop an IMU as a proof-of-concept for the INS.

The development of such an INS will require modular independent subsystems which can be individually upgraded and evolved without compromising the stability, precision, and safety of the overall system. It is toward this end that we designed the following architecture for Launch Vehicle Two (LV2).

Having observed both the present lack of advanced systems and the future need for those systems, it became apparent that an intermediate step was required. The development of a system with modular components would allow for the systematic qualification of subsystems needed for future launch capabilities. Extending the modularity idea to the airframe as well as the avionics will ensure that the entire system is scalable.

Of particular importance is the validation and testing of the IMU subsystem. The IMU sensor suite and the data streaming algorithms used to transmit and store that data need to be qualified for use with an INS system. Data from this system will be used to generate flight profiles for flight sequencing tests and flight path calculation in future rocket projects.

The initial development of LV2 embodies a clarification of the direction and goals of the PSAS. Rather than being an interim design on the path to an advanced system, LV2 will serve as a continuously upgradable modular design that allows the testing and validation of a wide range of avionics, payload, and airframe ideas.

The airframe design for LV2 will result in a modular launch vehicle which can be assembled into any configuration required for a flight. Fins, motor modules, and payload sections can be added, swapped, or removed, allowing for the testing and validation of various flight configurations. This modular approach will provide the PSAS with an evolvable launch vehicle which will serve as a testbed for avionics and propulsion design for years to come.

It should also be noted that for LV2 the concept of 'payload' has been redefined to a more traditional interpretation: a payload is an independent package carried by the rocket. The term was previously used to describe the flight control systems of the rocket, which will henceforth be known as 'avionics'. Payload development is outside of the scope of this document.

Development of the avionics package began with a functional decomposition of the overall system, which resulted in a number of functionally discrete system task blocks that must be accomplished in a successful flight. In keeping with our goal that the system be as modular as possible, the avionics team chose to embody each of these blocks as a separate subsystem. This will ensure that replacement of a subsystem will not affect other subsystems that are functionally distant. If each module has a clearly defined interface, individual subsystems can be swapped for upgrade or repair without affecting the overall functionality of the avionics system.