# MOPS/520 Product Manual

Document Revision 1.5

Document Part

96035-0105-00-0

# CONTENTS

| 1.                                                                                     | USER INFORMATION1                                                                                                                                 |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                                                                    | About This Manual1                                                                                                                                |

| 1.2                                                                                    | COPYRIGHT NOTICE                                                                                                                                  |

| 1.3                                                                                    | TRADEMARKS                                                                                                                                        |

| 1.4                                                                                    | WARRANTY                                                                                                                                          |

| 1.5                                                                                    | TECHNICAL SUPPORT                                                                                                                                 |

| 2.                                                                                     | INTRODUCTION                                                                                                                                      |

| 2.1                                                                                    | MOPS/520                                                                                                                                          |

| 3.                                                                                     | SPECIFICATIONS                                                                                                                                    |

| 3.1                                                                                    | FUNCTIONAL SPECIFICATIONS                                                                                                                         |

| 3.2                                                                                    | MECHANICAL SPECIFICATIONS                                                                                                                         |

| 3.3                                                                                    | ELECTRICAL SPECIFICATIONS                                                                                                                         |

| 3.4                                                                                    | ENVIRONMENTAL SPECIFICATIONS                                                                                                                      |

| 4.                                                                                     | CPU, CHIPSET, AND SUPER I/O7                                                                                                                      |

| 4.1                                                                                    | CPU7                                                                                                                                              |

| 4.2                                                                                    | CHIPSET7                                                                                                                                          |

| 4.3                                                                                    | SUPER I/O                                                                                                                                         |

| 5.                                                                                     | SYSTEM MEMORY7                                                                                                                                    |

| 6.                                                                                     | ISA AND PCI BUS EXPANSION                                                                                                                         |

| 6.1                                                                                    | CONNECTORS                                                                                                                                        |

| 6.2                                                                                    | PCI CONNECTOR (PC/104+)                                                                                                                           |

| 6.3                                                                                    | ADAPTER CARD MOUNTING                                                                                                                             |

| 6.4                                                                                    | I/O ADDRESS MAPPING LIMITATION                                                                                                                    |

| 7.                                                                                     | UNIVERSAL SERIAL BUS (USB) INTERFACE11                                                                                                            |

|                                                                                        | UNIVERSAL SERIAL DUS (USD) INTERFACE                                                                                                              |

| 7.1                                                                                    | USB1 AND USB2 CONNECTOR                                                                                                                           |

| 7.1<br>8.                                                                              |                                                                                                                                                   |

|                                                                                        | USB1 AND USB2 CONNECTOR11                                                                                                                         |

| <b>8.</b><br>8.1<br>8.2                                                                | USB1 AND USB2 CONNECTOR                                                                                                                           |

| <b>8.</b><br>8.1                                                                       | USB1 AND USB2 CONNECTOR                                                                                                                           |

| <b>8.</b><br>8.1<br>8.2                                                                | USB1 AND USB2 CONNECTOR                                                                                                                           |

| <b>8.</b><br>8.1<br>8.2<br>8.3                                                         | USB1 AND USB2 CONNECTOR                                                                                                                           |

| <ol> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>9.</li> </ol>                          | USB1 AND USB2 CONNECTOR                                                                                                                           |

| <ul> <li>8.</li> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>9.</li> <li>9.1</li> </ul> | USB1 AND USB2 CONNECTOR.11SERIAL COMMUNICATION INTERFACE12CONNECTORS12CONFIGURATION13LIMITATIONS14PARALLEL COMMUNICATION INTERFACE.15CONNECTORS15 |

| 10.1                                                                                                                                                                                                      | CONNECTOR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.                                                                                                                                                                                                       | FLOPPY DISK INTERFACE1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19                                                                                                                                                                     |

| 11.1                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                        |

| 11.2                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                        |

| 12.                                                                                                                                                                                                       | IDE INTERFACE2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                                                                                                                                     |

| 12.1                                                                                                                                                                                                      | CONNECTOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                                                                                                                                                                     |

| 13.                                                                                                                                                                                                       | ETHERNET INTERFACE2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21                                                                                                                                                                     |

| 13.1                                                                                                                                                                                                      | CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21                                                                                                                                                                     |

| 13.2                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                        |

| 13.3                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                        |

| 14.                                                                                                                                                                                                       | POWER2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24                                                                                                                                                                     |

| 14.1                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                        |

| 14.2                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                        |

| 14.3                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                        |

| 15.                                                                                                                                                                                                       | WATCHDOG TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25                                                                                                                                                                     |

| 15.1                                                                                                                                                                                                      | WATCHDOG BIOS INTERFACE2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25                                                                                                                                                                     |

| 16.                                                                                                                                                                                                       | CAN-BUS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27                                                                                                                                                                     |

| 16.1                                                                                                                                                                                                      | CONNECTOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27                                                                                                                                                                     |

|                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                        |

| 17.                                                                                                                                                                                                       | THE JIDA STANDARD2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                                                                                                     |

|                                                                                                                                                                                                           | THE JIDA STANDARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                        |

|                                                                                                                                                                                                           | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29                                                                                                                                                                     |

| 18.                                                                                                                                                                                                       | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>29</b><br>29                                                                                                                                                        |

| <b>18.</b><br>18.1                                                                                                                                                                                        | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>29</b><br>29<br>29<br>30                                                                                                                                            |

| <b>18.</b><br>18.1<br>18.2                                                                                                                                                                                | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>29</b><br>29<br>29<br>30                                                                                                                                            |

| <b>18.</b><br>18.1<br>18.2<br>18.3<br>18.4                                                                                                                                                                | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29<br>29<br>29<br>30<br>30                                                                                                                                             |

| <b>18.</b><br>18.1<br>18.2<br>18.3<br>18.4                                                                                                                                                                | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>29</b><br>29<br>29<br>30<br>30<br><b>30</b>                                                                                                                         |

| <ol> <li>18.</li> <li>18.1</li> <li>18.2</li> <li>18.3</li> <li>18.4</li> <li>19.</li> <li>19.1</li> <li>19.2</li> </ol>                                                                                  | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>29</li> <li>29</li> <li>30</li> <li>30</li> <li>30</li> <li>40</li> </ul>                                                                                     |

| <ol> <li>18.</li> <li>18.1</li> <li>18.2</li> <li>18.3</li> <li>18.4</li> <li>19.</li> <li>19.1</li> <li>19.2</li> <li>19.3</li> </ol>                                                                    | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS.       2         I/O PORT ASSIGNMENTS       2         INTERRUPT REQUEST LINES       2         DIRECT MEMORY ACCESS CHANNELS       3         UPPER MEMORY AREA MAP.       3         APPENDIX B: BIOS OPERATION       3         THE SETUP GUIDE.       3         BOOT UTILITIES       4         BIOS UPDATE WITH PHOENIX PHLASH.       4                                                                                                                                                                                      | <ul> <li>29</li> <li>29</li> <li>29</li> <li>30</li> <li>30</li> <li>30</li> <li>40</li> <li>42</li> </ul>                                                             |

| <ol> <li>18.</li> <li>18.1</li> <li>18.2</li> <li>18.3</li> <li>18.4</li> <li>19.</li> <li>19.1</li> <li>19.2</li> <li>19.3</li> <li>19.4</li> </ol>                                                      | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS.2I/O PORT ASSIGNMENTS2INTERRUPT REQUEST LINES2DIRECT MEMORY ACCESS CHANNELS3UPPER MEMORY AREA MAP.3APPENDIX B: BIOS OPERATION3THE SETUP GUIDE.3BOOT UTILITIES4BIOS UPDATE WITH PHOENIX PHLASH.4BOOT BLOCK SUPPORT4                                                                                                                                                                                                                                                                                                          | <ul> <li>29</li> <li>29</li> <li>29</li> <li>30</li> <li>30</li> <li>30</li> <li>40</li> <li>42</li> <li>43</li> </ul>                                                 |

| <ol> <li>18.</li> <li>18.1</li> <li>18.2</li> <li>18.3</li> <li>18.4</li> <li>19.</li> <li>19.1</li> <li>19.2</li> <li>19.3</li> <li>19.4</li> </ol>                                                      | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS.2I/O PORT ASSIGNMENTS2INTERRUPT REQUEST LINES2DIRECT MEMORY ACCESS CHANNELS3UPPER MEMORY AREA MAP.3APPENDIX B: BIOS OPERATION3THE SETUP GUIDE.3BOOT UTILITIES4BIOS UPDATE WITH PHOENIX PHLASH.4BOOT BLOCK SUPPORT4                                                                                                                                                                                                                                                                                                          | <ul> <li>29</li> <li>29</li> <li>29</li> <li>30</li> <li>30</li> <li>30</li> <li>40</li> <li>42</li> <li>43</li> </ul>                                                 |

| <ol> <li>18.</li> <li>18.1</li> <li>18.2</li> <li>18.3</li> <li>18.4</li> <li>19.</li> <li>19.1</li> <li>19.2</li> <li>19.3</li> <li>19.4</li> </ol>                                                      | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS.       2         I/O PORT ASSIGNMENTS       2         INTERRUPT REQUEST LINES       2         DIRECT MEMORY ACCESS CHANNELS       3         UPPER MEMORY AREA MAP.       3         APPENDIX B: BIOS OPERATION       3         THE SETUP GUIDE.       3         BOOT UTILITIES       4         BIOS UPDATE WITH PHOENIX PHLASH       4         BOOT BLOCK SUPPORT       4         APPENDIX C: CONNECTORS.       4                                                                                                            | <ul> <li>29</li> <li>29</li> <li>29</li> <li>30</li> <li>30</li> <li>30</li> <li>40</li> <li>42</li> <li>43</li> <li>44</li> </ul>                                     |

| <ol> <li>18.</li> <li>18.1</li> <li>18.2</li> <li>18.3</li> <li>18.4</li> <li>19.</li> <li>19.1</li> <li>19.2</li> <li>19.3</li> <li>19.4</li> <li>20.</li> <li>20.1</li> </ol>                           | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS       2         I/O PORT ASSIGNMENTS       2         INTERRUPT REQUEST LINES       2         DIRECT MEMORY ACCESS CHANNELS       3         UPPER MEMORY AREA MAP       3         APPENDIX B: BIOS OPERATION       3         THE SETUP GUIDE       3         BOOT UTILITIES       4         BIOS UPDATE WITH PHOENIX PHLASH.       4         BOOT BLOCK SUPPORT       4         APPENDIX C: CONNECTORS       4                                                                                                               | <ul> <li>29</li> <li>29</li> <li>30</li> <li>30</li> <li>30</li> <li>40</li> <li>42</li> <li>43</li> <li>44</li> </ul>                                                 |

| <ol> <li>18.</li> <li>18.1</li> <li>18.2</li> <li>18.3</li> <li>18.4</li> <li>19.</li> <li>19.1</li> <li>19.2</li> <li>19.3</li> <li>19.4</li> <li>20.</li> <li>20.1</li> <li>21.</li> </ol>              | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS.       2         I/O PORT ASSIGNMENTS       2         INTERRUPT REQUEST LINES       2         DIRECT MEMORY ACCESS CHANNELS       3         UPPER MEMORY AREA MAP.       3         APPENDIX B: BIOS OPERATION       3         THE SETUP GUIDE       3         BOOT UTILITIES       4         BIOS UPDATE WITH PHOENIX PHLASH.       4         BOOT BLOCK SUPPORT       4         APPENDIX C: CONNECTORS.       4         CONNECTOR LAYOUT.       4                                                                          | <ul> <li>29</li> <li>29</li> <li>30</li> <li>30</li> <li>30</li> <li>40</li> <li>42</li> <li>43</li> <li>44</li> <li>45</li> </ul>                                     |

| <ol> <li>18.</li> <li>18.1</li> <li>18.2</li> <li>18.3</li> <li>18.4</li> <li>19.</li> <li>19.1</li> <li>19.2</li> <li>19.3</li> <li>19.4</li> <li>20.</li> <li>20.1</li> <li>21.</li> </ol>              | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS.       2         I/O PORT ASSIGNMENTS       2         INTERRUPT REQUEST LINES       2         DIRECT MEMORY ACCESS CHANNELS       3         UPPER MEMORY AREA MAP.       3         APPENDIX B: BIOS OPERATION       3         THE SETUP GUIDE.       3         BOOT UTILITIES       4         BIOS UPDATE WITH PHOENIX PHLASH.       4         BOOT BLOCK SUPPORT       4         APPENDIX C: CONNECTORS.       4         APPENDIX D: BLOCK DIAGRAM       4         APPENDIX E: LIMITATIONS       4                         | <ul> <li>29</li> <li>29</li> <li>29</li> <li>30</li> <li>30</li> <li>30</li> <li>40</li> <li>42</li> <li>43</li> <li>44</li> <li>45</li> <li>46</li> </ul>             |

| <ol> <li>18.</li> <li>18.1</li> <li>18.2</li> <li>18.3</li> <li>18.4</li> <li>19.</li> <li>19.1</li> <li>19.2</li> <li>19.3</li> <li>19.4</li> <li>20.</li> <li>20.1</li> <li>21.</li> <li>22.</li> </ol> | APPENDIX A: SYS TEM RESOURCE ALLOCATIONS       2         I/O PORT ASSIGNMENTS       2         INTERRUPT REQUEST LINES       2         DIRECT MEMORY ACCESS CHANNELS       3         UPPER MEMORY AREA MAP.       3         APPENDIX B: BIOS OPERATION       3         THE SETUP GUIDE.       3         BOOT UTILITIES       4         BIOS UPDATE WITH PHOENIX PHLASH.       4         BOOT BLOCK SUPPORT       4         APPENDIX C: CONNECTORS.       4         CONNECTOR LAYOUT.       4         APPENDIX D: BLOCK DIAGRAM       4         PARALLEL PORT.       4 | <ul> <li>29</li> <li>29</li> <li>29</li> <li>30</li> <li>30</li> <li>40</li> <li>42</li> <li>43</li> <li>44</li> <li>45</li> <li>46</li> <li>46</li> <li>46</li> </ul> |

| 22.4    | SYSTEM CLOCK DEVIATION                 | 47 |

|---------|----------------------------------------|----|

| 22.5    | WINDOWS <sup>®</sup> 2000 SUPPORT      | 47 |

| 22.6    | ISA SCSI SUPPORT                       |    |

| 22.7    | VIDEO SUPPORT                          | 47 |

| 22.8    | WATCHDOG NMI HANDLING                  |    |

| 23. API | PENDIX F: LITERATURE, STANDARDS, LINKS | 49 |

| 23.1    | PC/104-Bus                             | 49 |

| 23.2    | ISA-BUS, STANDARD PS/2 CONNECTORS      |    |

| 23.3    | PCI SPECIFICATIONS                     |    |

| 23.4    | RS232C                                 |    |

| 23.5    | USB                                    |    |

| 24. API | PENDIX G: CONTACT INFORMATION          | 51 |

| 24.1    | EUROPE                                 | 51 |

| 24.2    | NORTH AND SOUTH AMERICA                | 51 |

| 24.3    | ASIA                                   | 51 |

| 25. API | PENDIX H: DOCUMENT REVISION HISTORY    | 52 |

# 1. USER INFORMATION

## **1.1 About This Manual**

This document is designed to provide information about products from JUMP*tec*® Industrielle Computertechnik AG (JUMP*tec*®) and/or its subsidiaries. No warranty of suitability, purpose, or fitness is implied. While every attempt has been made to insure the information in this document is accurate, the information contained within is supplied "as-is" and is subject to change without notice.

For the circuits, descriptions and tables indicated, JUMP*tec*® assumes no responsibility as far as patents or other rights of third parties are concerned.

#### 1.1.1 Adastra Systems Brand

Adastra Systems Corporation became a wholly owned subsidiary of JUMP*tec*® Industrielle Computertechnik AG in February 2000, and changed their name to JUMP*tec*® Adastra in the following year. Products labeled and sold under the Adastra Systems or JUMP*tec*® Adastra names are now considered JUMP*tec*® product for all practical purposes, including warranty and support.

## 1.2 Copyright Notice

Copyright © 2001 JUMPtec® Industrielle Computertechnik AG.

Copyright © 2001 JUMPtec® Adastra Corporation.

All rights reserved. No part of the contents of this manual may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), without the express written permission of JUMP*tec*® Industrielle Computertechnik AG or JUMP*tec*® Adastra Corporation.

## 1.3 Trademarks

- JUMP*tec*® is the registered trademark of Jumptec Industrielle Computertechnik AG.

- Adastra Systems and JUMP*tec*® Adastra are a trademarks of Adastra Systems Corporation.

- AT and IBM are trademarks of International Business Machines.

- XT, AT, PS/2 and Personal System/2 are trademarks of International Business Machines Corporation.

- Microsoft is a registered trademark of Microsoft Corporation.

• Intel is a registered trademark of Intel Corporation.

All other products and trademarks mentioned in this manual are trademarks of their respective owners.

## 1.4 Warranty

This JUMP*tec*<sup>®</sup> product is warranted against defects in material and workmanship for the warranty period from the date of shipment. During the warranty period, JUMP*tec*<sup>®</sup> will at its discretion decide either to repair or replace defective products.

Within the warranty period, the repair of products is free of charge as long as the warranty conditions are observed.

**NOTE:** Due to the high cost of testing, you will be charged with the cost of the test if no fault is found. Repair after the warranty period will be charged.

For warranty service or repair, the product must be returned to a service facility designated by JUMP*tec*®.

The warranty will not apply to defects resulting from improper or inadequate maintenance or handling by the buyer, unauthorized modification or misuse, operation outside of the product's environmental specifications or improper installation or maintenance.

JUMP*tec*® will not be responsible for any defects or damages to other products not supplied by JUMP*tec*® that are caused by a faulty JUMP*tec*® product.

# 1.5 Technical Support

Technicians and engineers from JUMP*tec*® and/or its subsidiaries are available for technical support. We are committed to making our product easy to use and will help in any way we can when you use our products in your systems.

Before contacting JUMP*tec*® technical support, please consult our web site for the latest available product documentation, utilities, and drivers. If the information provided there does not help to solve the problem, contact us by email or telephone. The contact information for technical support in your area is located in Appendix G: Contact Information.

# 2. INTRODUCTION

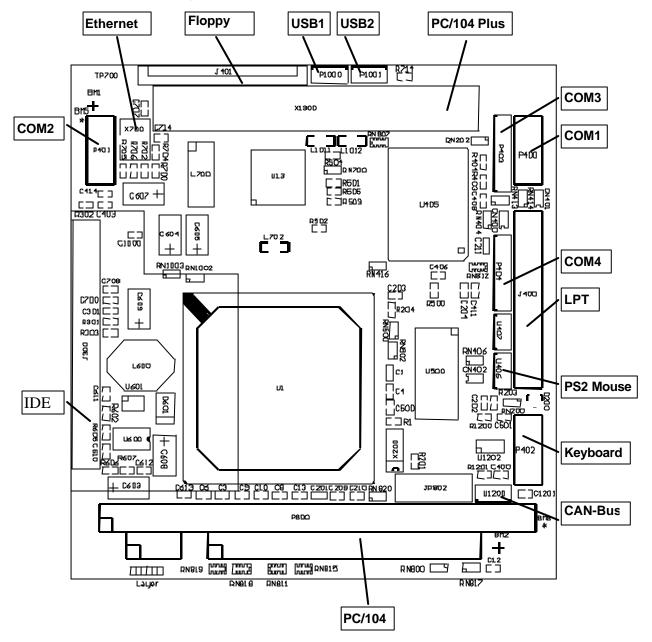

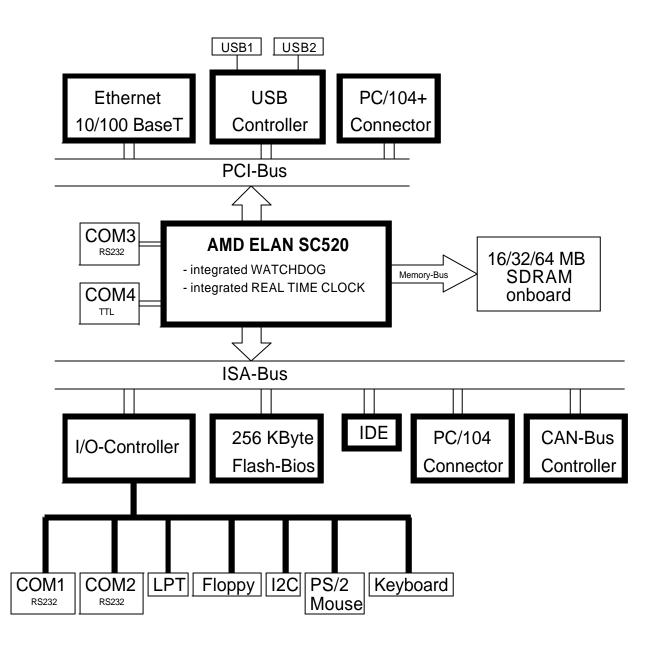

## 2.1 MOPS/520

The *MOPS/520* is based on the ÉlanSC520 microcontroller (32-bit Am5x86® CPU). It integrates the complete functionality of motherboard with CPU, System-BIOS, up to 64 MByte SDRAM, keyboard-controller, real time clock and additional peripheral functions like COM1..COM4, LPT1, Floppy-interface, IDE-harddisk-interface, Watchdog, Ethernet access and optional CAN-Bus interface. The system runs with CPU clock speed 100 MHz or 133MHz.

# 3. SPECIFICATIONS

## 3.1 Functional Specifications

- Processor Support: 32-bit Am5x86® CPU with 16 KByte write-back-Cache

- Memory: 16/32/64MB SDRAM (onboard)

- BIOS: Phoenix, 256 KByte Flash

- Serial: Three 16550 RS232C, plus one TTL

- Parallel: One port, with ECP/EPP support

- USB: Two ports

- Network: Davicom DM9102A network controller 32-bit Fast Ethernet, 100/10BASET, auto-negotiated

- Bus Expansion: PC/104-Plus ISA/PCI bus connection, 4 ISA PC/104 card drive capability, 4 PC/104*Plus* card drive capability

- IDE: One IDE interface, supporting two drives and JUMPtec® CHIPdisk

- Floppy: Dual floppy support

- Keyboard and PS/2 Mouse

- Real-time Clock: With external Battery-support

- Watchdog Timer

- CAN Bus Interface (optional): Intel® 82527 Controller

- 5V only operation

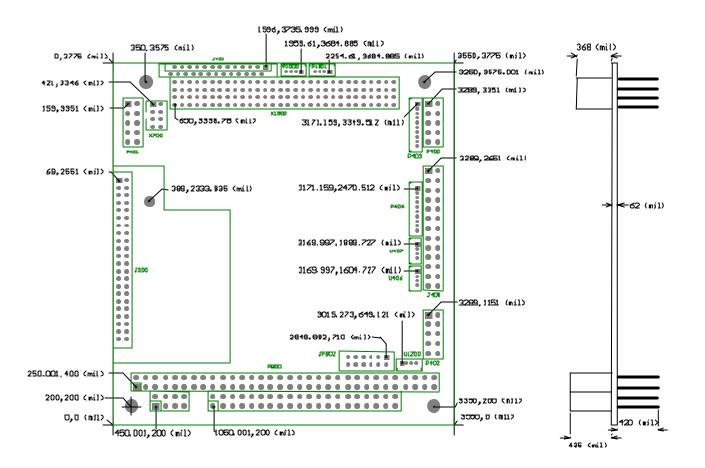

## 3.2 Mechanical Specifications

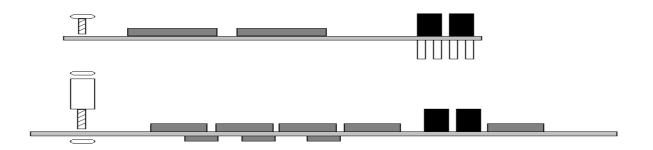

- Mechanical: 3.7" x 3.5 "

- Mounting: 2 pieces of 2x32 pin male and 2x20 pin male connector

- PC/104plus: 4 x 30 pin 2mm connector

The PC/104plus connector is without connector shroud. It's not possible to use a PC/104plus board with connector shroud at top at MOPS/520. This is only a mechanical limitation and does not reduce the functionality of MOPS/520. Please order a module without connector shroud or place MOPS/520 at top at the stack.

## **3.3 Electrical Specifications**

#### 3.3.1 Supply Voltage

• 5V DC +/- 5%

#### 3.3.2 Supply Voltage Ripple

• 100 mV peak to peak 0 - 20 MHz

#### 3.3.3 Supply Current

- Typical: 1.7A

- Maximum: 1.7A

#### 3.3.4 External RTC Battery

- External RTC battery voltage 2.0 3.3V (typ. 2.5V)

- External RTC battery quiescent current typ. 5uA

## 3.4 Environmental Specifications

#### Temperature:

• Operating:  $0 \text{ to } + 60^{\circ}\text{C}$

The max. case temperature of diode D601 is specified with 70°C. For the detailed location of D601 see Appendix C (section 20.)

- Non-operating:  $-10 \text{ to} + 85 \circ \text{C}$

- Humidity: Operating: 10% to 90% (non-condensing)

- Non-operating: 5% to 95% (non-condensing)

# 4. CPU, CHIPSET, AND SUPER I/O

# 4.1 CPU

The *MOPS/520* supports the AMD ÉlanSC520 processor with clock speeds up to 133MHz. This is integrated 32-Bit Microcontroller provides following features:

- Synchronous DRAM (SDRAM) controller

- 33 MHz, 32-bit PCI bus Revision 2.2-compliant

- 100-MHz and 133-MHz operating frequencies

- PCI 3.3V/5V tolerance interface

- Low-voltage operation (core V CC = 2.5 V)

- 5-V tolerant I/O (3.3-V output levels)

- 16-Kbyte write-back cache

- Enhanced DMA controller includes double buffer chaining, extended address and transfer counts, and flexible channel routing

- Two 16550-compatible UARTs operate at baud rates up to 1.15 Mbit/s with optional DMA interface

- Programmable interval timer (PIT)

- Real-time clock (RTC) with battery backup capability and 114 bytes of RAM

- Watchdog timer guards against runaway software

- Native support for pSOS, QNX, RTXC, VxWorks, and Windows<sup>®</sup> CE operating systems

- Enhanced programmable interrupt controller (PIC) prioritizes 22 interrupt levels (up to 15 external sources) with flexible routing

# 4.2 Chipset

The *MOPS/520* contains the ÉlanSC520 micro controller chipset.

## 4.3 Super I/O

The *MOPS/520* contains one Winbond W83977F Super I/O chip.

# 5. SYSTEM MEMORY

The system memory of the *MOPS/520* consists of an onboard SDRAM. It is available in 16, 32, or 64 Megabyte configurations. The memory configuration is set by the factory and cannot be altered.

# 6. ISA AND PCI BUS EXPANSION

For expansion, the *MOPS/520* provides a PC/104-*Plus* socket. This industry standard bus provides both ISA and PCI bus signals. The PC/104-*Plus* standard is downward compatible with PC/104 and enables the use of standard PC/104 and PC/104-*Plus* adapter cards.

# 6.1 Connectors

J10 is a 64-pin, dual row socket connector, with 0.1" x 0.1" pitch, which implements the standard 8-bit ISA bus signals. J11 is a 40-pin connector of the same style and implements the ISA bus 16-bit expansion signals. All ISA bus signals are supported.

| ISA-LOWER/J10 |         |       |           | ISA-UPPER/J11 |        |       |              |

|---------------|---------|-------|-----------|---------------|--------|-------|--------------|

| PIN #         | SIGNAL  | PIN # | SIGNAL    | PIN #         | SIGNAL | PIN # | SIGNAL       |

| A1            | VOCHK   | B1    | GND       | C0            | GND    | D0    | GND          |

| A2            | SD7     | B2    | RESDRV    | C1            | \BHE   | D1    | \MEMCS16     |

| A3            | SD6     | B3    | VCC (***) | C2            | LA23   | D2    | VOCS16       |

| A4            | SD5     | B4    | IRQ9      | C3            | LA22   | D3    | IRQ10        |

| A5            | SD4     | B5    | -5V       | C4            | LA21   | D4    | IRQ11        |

| A6            | SD3     | B6    | DREQ2     | C5            | LA20   | D5    | IRQ12        |

| A7            | SD2     | B7    | -12V      | C6            | LA19   | D6    | IRQ15(**)    |

| A8            | SD1     | B8    | \WS0      | C7            | LA18   | D7    | IRQ14        |

| A9            | SD0     | B9    | +12V      | C8            | LA17   | D8    | \DACK0(**)   |

| A10           | IOCHRDY | B10   | GND (*)   | C9            | \MEMR  | D9    | DREQ0 (**)   |

| A11           | AEN     | B11   | \SMEMW    | C10           | \MEMW  | D10   | \DACK5       |

| A12           | SA19    | B12   | \SMEMR    | C11           | SD8    | D11   | DREQ5        |

| A13           | SA18    | B13   | \IOW      | C12           | SD9    | D12   | \DACK6 (**)  |

| A14           | SA17    | B14   | VOR       | C13           | SD10   | D13   | DREQ6 (**)   |

| A15           | SA16    | B15   | \DACK3    | C14           | SD11   | D14   | \DACK7 (**)  |

| A16           | SA15    | B16   | DREQ3     | C15           | SD12   | D15   | DREQ7 (**)   |

| A17           | SA14    | B17   | \DACK1    | C16           | SD13   | D16   | VCC (***)    |

| A18           | SA13    | B18   | DREQ1     | C17           | SD14   | D17   | \MASTER (**) |

| A19           | SA12    | B19   | \REFSH    | C18           | SD15   | D18   | GND          |

| A20           | SA11    | B20   | SYSCLK    | C19           | KEY(*) | D19   | GND          |

| A21           | SA10    | B21   | IRQ7      |               |        |       |              |

| A22           | SA9     | B22   | IRQ6      |               |        |       |              |

| A23           | SA8     | B23   | IRQ5      |               |        |       |              |

| A24           | SA7     | B24   | IRQ4      |               |        |       |              |

| A25           | SA6     | B25   | IRQ3      |               |        |       |              |

| A26           | SA5     | B26   | \DACK2    |               |        |       |              |

| A27           | SA4     | B27   | TC        |               |        |       |              |

| A28           | SA3     | B28   | ALE       |               |        |       |              |

| A29           | SA2     | B29   | VCC (***) |               |        |       |              |

| A30           | SA1     | B30   | OSC       | 7             |        |       |              |

| A31           | SA0     | B31   | GND       |               |        |       |              |

| A32           | GND     | B32   | GND       | 7             |        |       |              |

(\*) - Key pin for PC/104; GND for PC/104+ specification

(\*\*) - Not supported on MOPS/520 boards

(\*\*\*) - To protect the external powerlines of peripheral devices the customer has to take care about:

that the wires have the right diameter to withstand the maximum available current

that the enclosure of the peripheral device fulfils the fire protecting requirements of IEC/EN 60950.

J12 is a quad row socket connector, with 2mm x 2mm pitch, which implements the standard 32-bit PCI bus signals.

# 6.2 PCI Connector (PC/104+)

| Pin | Signal name   | Signal Name | Signal Name   | Signal Name   |

|-----|---------------|-------------|---------------|---------------|

|     | A             | В           | С             | D             |

| 1   | GND           | Reserved    | VCC (**)      | AD00          |

| 2   | VCC (**)      | AD02        | AD01          | AD03          |

| 3   | AD05          | GND         | AD04          | AD03          |

| 4   | C/BE0         | AD07        | GND           | AD06          |

| 5   | GND           | AD09        | AD08          | GND           |

| 6   | AD11          | VCC (**)    | AD10          | GND           |

| 7   | AD14          | AD13        | GND           | AD12          |

| 8   | VCC3 (*)      | C/BE1       | AD15          | VCC3 (*)      |

| 9   | SERR          | GND         | SB0           | PAR           |

| 10  | GND           | PERR        | VCC3 (*)      | SDONE         |

| 11  | STOP          | VCC3 (*)    | LOCK          | GND           |

| 12  | VCC3 (*)      | TRDY        | GND           | DEVSEL        |

| 13  | FRAME         | GND         | IRDY          | VCC3 (*)      |

| 14  | GND           | AD16        | VCC3 (*)      | C/BE2         |

| 15  | AD18          | VCC3 (*)    | AD17          | GND           |

| 16  | AD21          | AD20        | GND           | AD19          |

| 17  | VCC3 (*)      | AD23        | AD22          | VCC3 (*)      |

| 18  | IDSEL0 (AD20) | GND         | IDSEL1 (AD21) | IDSEL2 (AD22) |

| 19  | AD24          | C/BE3       | VI/O          | IDSEL3 (AD23) |

| 20  | GND           | AD26        | AD25          | GND           |

| 21  | AD29          | VCC (**)    | AD28          | AD27          |

| 22  | VCC (**)      | AD30        | GND           | AD31          |

| 23  | REQ0          | GND         | REQ1          | VI/O          |

| 24  | GND           | REQ2        | VCC (**)      | GNT0          |

| 25  | GNT1          | VI/O        | GNT2          | GND           |

| 26  | VCC (**)      | CLK0        | GND           | CLK1          |

| 27  | CLK2          | VCC (**)    | CLK3          | GND           |

| 28  | GND           | INTD        | VCC (**)      | RST           |

| 29  | +12V          | INTA        | INTB          | INTC          |

| 30  | -12V          | Reserved    | Reserved      | Reserved      |

(\*) - NOT SUPPORTED ON MOPS/520

(\*\*) - To protect the external powerlines of peripheral devices the customer has to take care about:

- that the wires have the right diameter to withstand the maximum available current

- that the enclosure of the peripheral device fulfils the fire protecting requirements of IEC/EN 60950.

For signal description and peripheral driver current, refer to the PC/104+SPECification.

# 6.3 Adapter Card Mounting

PC/104 and PC/104-*Plus* adapter cards are mounted in a "stack-through" manner. Adapter cards are designed with plugs on their undersides that mate with the PC/104 socket connectors of *MOPS/520*. PC/104 adapters can support the socket connector version on their topside and allow further "stacking" of adapters.

# 6.4 I/O Address Mapping Limitation

Only I/O addresses below 400h are mapped to the external ISA respectively PC104 bus. All higher I/O addresses are directed to PCI.

# 7. UNIVERSAL SERIAL BUS (USB) INTERFACE

The *MOPS/520* comes with two USB ports and further expansion may be achieved by adding external hubs. Technically, up to 127 individual USB peripherals can be connected at one time.

# 7.1 USB1 and USB2 Connector

| PIN | PIN FUNCTION |

|-----|--------------|

| 1   | +5V          |

| 2   | USB-         |

| 3   | USB+         |

| 4   | GND          |

The power contacts on PIN 1 and 4 are only usable for internal USB devices. It is strictly recommended to use a fuse for power on external USB connectors.

# 8. SERIAL COMMUNICATION INTERFACE

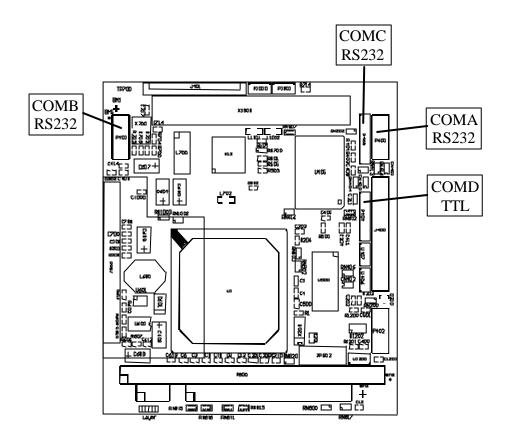

The *MOPS/520* has four 16550-compatible serial ports, COMA, COMB, COMC and COMD. The line drivers used for COMA through COMC conform to the IEEE RS-232C standard. COMD is a TTL-level interface.

## 8.1 Connectors

|     | COMA, COMB, COMC (RS232C) AND COMD (TTL) |             |                           |                          |  |  |  |

|-----|------------------------------------------|-------------|---------------------------|--------------------------|--|--|--|

| PIN | SIGNALNAME                               | IN /<br>OUT | DSUB-25<br>(NEED ADAPTER) | DSUB-9<br>(NEED ADAPTER) |  |  |  |

| 1   | DCD                                      | In          | 8                         | 1                        |  |  |  |

| 2   | DSR                                      | In          | 6                         | 6                        |  |  |  |

| 3   | RxD                                      | In          | 3                         | 2                        |  |  |  |

| 4   | RTS                                      | Out         | 4                         | 7                        |  |  |  |

| 5   | TxD                                      | Out         | 2                         | 3                        |  |  |  |

| 6   | CTS                                      | In          | 5                         | 8                        |  |  |  |

| 7   | DTR                                      | Out         | 20                        | 4                        |  |  |  |

| 8   | RI                                       | In          | 22                        | 9                        |  |  |  |

| 9   | GND                                      |             | 7                         | 5                        |  |  |  |

| 10  | VCC (*)                                  |             |                           |                          |  |  |  |

For signal descriptions, please refer to additional literature.

(\*) - To protect the external powerlines of peripheral devices the customer has to take care about:

- that the wires have the right diameter to withstand the maximum available current

- that the enclosure of the peripheral device fulfils the fire protecting requirements of IEC/EN 60950.

The serial ports are completely compatible with the serial port implementation used on the IBM Serial Adapter.

# 8.2 Configuration

COMA and COMB can be set to several I/O-addresses and IRQs in the setup. COMC and COMD are fix-mapped to the addresses and IRQs. See the table below for more information.

| SERIAL<br>PORT | POSSIBLE I/O-<br>ADDRESSES | POSSIBLE<br>IRQS |

|----------------|----------------------------|------------------|

| COMA           | 3F8h, 2F8h, 3E8h,          | 3, 4, 10         |

|                | 2E8h                       |                  |

| COMB           | 3F8h, 2F8h, 3E8h,          | 3, 4, 11         |

|                | 2E8h                       |                  |

| COMC           | 3F8h                       | 4                |

| COMD           | 2F8                        | 3                |

Please Note: Most OS detect the serial port with the I/O-address 3F8h as COM1 and 2F8h as COM2. Therefore, if COMC and COMD are enabled they will be detected as COM1 and COM2.

# 8.3 Limitations

The SC520 integrated serial ports (serial port C and D on the MOPS/520) show two deviations from the standard UART behaviour:

The delta ring indicator bit in the modem status register (bit 2) is only set when the ring indicator signal has changed from an active to an inactive state since the last time the modem status register was read.

Usually this bit is set for RI changes from inactive to active as well.

In 16550 compatible mode a received data interrupt is generated when the very first data byte of a continuous data stream is placed in FIFO. This error only occurs for the first character of a continuous data stream received by the UART. Following the FIFO time-out interrupt for the first character received, the remainder of the data stream will be indicated according to the trigger value set in the RFRT bits of the UART FIFO control registers.

# 9. PARALLEL COMMUNICATION INTERFACE

The *MOPS/520* supports one enhanced parallel port. ECP and EPP modes are supported.

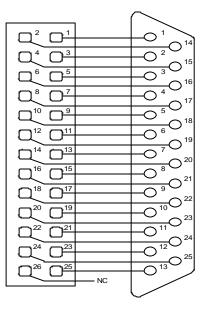

## 9.1 Connectors

| PARALLEL PORT LPT 1 |            |                  |          |                           |  |  |

|---------------------|------------|------------------|----------|---------------------------|--|--|

| PIN                 | SIGNALNAME | FUNCTION         | IN / OUT | DSUB-25<br>(NEED ADAPTER) |  |  |

| 1                   | /Strobe    |                  | Out      | 1                         |  |  |

| 3                   | Data 0     |                  | I/O      | 2                         |  |  |

| 5                   | Data 1     |                  | I/O      | 3                         |  |  |

| 7                   | Data 2     |                  | I/O      | 4                         |  |  |

| 9                   | Data 3     |                  | I/O      | 5                         |  |  |

| 11                  | Data 4     |                  | I/O      | 6                         |  |  |

| 13                  | Data 5     |                  | I/O      | 7                         |  |  |

| 15                  | Data 6     |                  | I/O      | 8                         |  |  |

| 17                  | Data 7     |                  | I/O      | 9                         |  |  |

| 19                  | /ACK       |                  | in       | 10                        |  |  |

| 21                  | BUSY       |                  | in       | 11                        |  |  |

| 23                  | PAPER out  |                  | in       | 12                        |  |  |

| 25                  | SEL out    |                  | in       | 13                        |  |  |

| 2                   | /AUTOFD    |                  | out      | 14                        |  |  |

| 4                   | /ERROR     |                  | in       | 15                        |  |  |

| 6                   | /INIT      |                  | out      | 16                        |  |  |

| 8                   | SEL in     |                  | out      | 17                        |  |  |

| 26                  | VCC (*)    | + 5 V            |          | NC                        |  |  |

| 10,12               | GND        | Signal<br>Ground |          | 18 - 25                   |  |  |

| 14,16               | GND        | Signal<br>Ground |          | 18 - 25                   |  |  |

| 18,20               | GND        | Signal<br>Ground |          | 18 - 25                   |  |  |

| 22,24               | GND        | Signal<br>Ground |          | 18 - 25                   |  |  |

For signal description please refer to additional literature.

(\*) - To protect the external powerlines of peripheral devices the customer has to take care about:

- that the wires have the right diameter to withstand the maximum available current

- that the enclosure of the peripheral device fulfils the fire protecting requirements of IEC/EN 60950.

The Centronics printer interface can be programmed via the system setup menu. Refer to the peripheral setup for more information. The parallel port is completely compatible with the parallel port implementation used in the IBM PS-II-Parallel Adapter.

An adapter cable may be used to change from the 26-pin header style of the *MOPS/520* to the more common 25-pin female D-sub.

26-pin Header to 25-pin D-Sub conversion

# 9.2 Configuration

The *MOPS/520* parallel ports are fully bi-directional. The bi-directional functions are compatible with those of a PS/2 style parallel port. This functionality is always available and does not conflict with normal printer use. The parallel port mode, I/O addresses, and IRQs are defined in the BIOS Setup utility.

# 9.3 Limitations

Due to chipset limitations, parallel port mode ECP as well as parallel port base address 3BCh (in any mode) cannot be used when a PCI video adapter is installed on the system. With ISA video adapters these restrictions do not apply

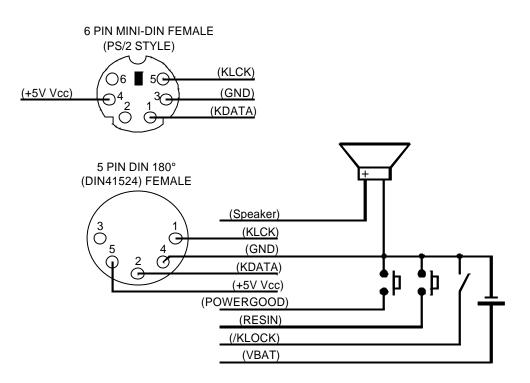

# **10. FRONT PANEL INTERFACE**

The Front Panel Interface consists of the following: Keyboard, Reset, Battery, Speaker.

# 10.1 Connector

| PIN | SIGNAL NAME | FUNCTION               | 5-PIN DIODE<br>KEYBOARD<br>ADAPTER | 6-PIN MINIDIN<br>KEYBOARD<br>ADAPTER (PS2) |

|-----|-------------|------------------------|------------------------------------|--------------------------------------------|

| 1   | SPKR        | Speaker output         |                                    |                                            |

| 2   | GND         | Ground                 |                                    |                                            |

| 3   | RESIN       | Reset input 1          |                                    |                                            |

| 4   | /KLOCK      | Keyboard lock          |                                    |                                            |

| 5   | KDATA       | Keyboard data          | 2                                  | 1                                          |

| 6   | KCLK        | Keyboard clock         | 1                                  | 5                                          |

| 7   | GND         | Ground                 | 4                                  | 3                                          |

| 8   | VCC (*)     | +5V                    | 5                                  | 4                                          |

| 9   | VBAT        | VBAT input (max. 3,3V) |                                    |                                            |

| 10  | POWERGOOD   | Reset input 2          |                                    |                                            |

(\*) - To protect the external powerlines of peripheral devices the customer has to take care about:

- that the wires have the right diameter to withstand the maximum available current

- that the enclosure of the peripheral device fulfils the fire protecting requirements of IEC/EN 60950.

#### /KLOCK (keyboard lock)

- Input on CPU modules

- Output on any other module

- Input to the keyboard controller: input port 1 bit 7

#### RESIN (reset input 1)

- Input on CPU modules

- Open collector output on all other modules

- When the power good goes high, it starts the reset generator on the CPU module to pull the onboard reset line high after a valid reset period. This pin can also be used as a low active hardware reset for modules.

#### SPKR (speaker output)

- Open collector output on modules that can drive a loudspeaker

- Input on modules which connects an 8-Ohm loudspeaker to this pin.

- An 8-Ohm loudspeaker is connected between SPEAKER and GND. Only one loudspeaker should be connected to this pin. Usually only the CPU drives this pin, however other modules can also use this signal to drive the system loudspeaker.

#### KDATA (keyboard data)

- Bi-directional I/O pin on CPU modules

- Keyboard data signal

#### KCLK (keyboard clock)

- Bi-directional I/O pin on CPU modules

- Keyboard clock signal

#### VBAT (system battery connection)

- This pin connects a system battery to all modules.

- The battery voltage has to be higher than 2.0V and lower than 3.3V. A 3V battery is recommended.

- Note that there is no battery needed to hold the CMOS-setup data. Your configuration concerning hard disks, floppy drives etc. is automatically saved in an onboard FRAM. However, the battery is necessary to serve the CMOS date and time while power consumption is turned off.

#### POWERGOOD (reset input 2)

- Input on CPU modules

- Open collector output on all other modules

- When power good goes high, it starts the reset generator on the CPU module to pull the onboard reset line high after a valid reset period. This pin can also be used as a low active hardware reset for modules.

# 11. FLOPPY DISK INTERFACE

The floppy disk interface can support one 3.5" drive, using the adapter cable ADA-Floppy 2, (part number 96001-0000-00-0). Supported drive capacities are 720K, 1.44M, or 2.88M.

# 11.1 Connector

| PIN | Signal  | Function | Pin | Signal | Function         |

|-----|---------|----------|-----|--------|------------------|

| 1   | VCC (*) | + 5V     | 2   | IDX    | Index            |

| 3   | VCC (*) | + 5V     | 4   | DS0    | Drive select 0   |

| 5   | VCC (*) | + 5V     | 6   | /DCHNG | Disk change      |

| 7   | NC      | -        | 8   | NC     | -                |

| 9   | NC      | -        | 10  | Mo0    | Motor on         |

| 11  | NC      | -        | 12  | DIR    | Direction select |

| 13  | NC      | -        | 14  | STEP   | Step             |

| 15  | GND     | Ground   | 16  | WD     | Write data       |

| 17  | GND     | Ground   | 18  | WG     | Write gate       |

| 19  | GND     | Ground   | 20  | TR00   | Track 00         |

| 21  | GND     | Ground   | 22  | WP     | Write protect    |

| 23  | GND     | Ground   | 24  | RD     | Read data        |

| 25  | GND     | Ground   | 26  | SIDE   | Side one select  |

(\*) - To protect the external powerlines of peripheral devices the customer has to take care about:

- that the wires have the right diameter to withstand the maximum available current

- that the enclosure of the peripheral device fulfils the fire protecting requirements of IEC/EN 60950.

For signal descriptions, please refer to additional literature.

# **11.2 Configuration**

The drive type must be specified using the BIOS Setup utility. The 3.5" drive type can be 720KB, 1.44MB, 2.44MB, or NONE. The floppy disk interface can be disabled in BIOS Setup.

# 12. IDE INTERFACE

The *MOPS/520* contains one IDE interface capable of driving two hard disks. When two devices are connected to a single adapter, they are connected in a typical Master/Slave, daisy chain fashion.

## 12.1 Connector

IDE connector is a 44-pin, dual in-line, 2mm pitch, and male header.

One or two IDE drives may be connected to the header by using the appropriate flat ribbon cable. The first drive must be configured as the master; the second drive (at the end of the cable) must be configured as the slave. Consult the disk drive manual for instructions on this task.

|     | IDE CONNECTOR FOR 2.5 " HARD DISK |     |         |  |  |  |  |

|-----|-----------------------------------|-----|---------|--|--|--|--|

| PIN | SIGNAL                            | PIN | SIGNAL  |  |  |  |  |

| 1   | /RESET                            | 2   | GND     |  |  |  |  |

| 3   | D7                                | 4   | D8      |  |  |  |  |

| 5   | D6                                | 6   | D9      |  |  |  |  |

| 7   | D5                                | 8   | D10     |  |  |  |  |

| 9   | D4                                | 10  | D11     |  |  |  |  |

| 11  | D3                                | 12  | D12     |  |  |  |  |

| 13  | D2                                | 14  | D13     |  |  |  |  |

| 15  | D1                                | 16  | D14     |  |  |  |  |

| 17  | D0                                | 18  | D15     |  |  |  |  |

| 19  | GND                               | 20  | NC      |  |  |  |  |

| 21  | NC                                | 22  | GND     |  |  |  |  |

| 23  | /IOW                              | 24  | GND     |  |  |  |  |

| 25  | /IOR                              | 26  | GND     |  |  |  |  |

| 27  | NC                                | 28  | BALE    |  |  |  |  |

| 29  | NC                                | 30  | GND     |  |  |  |  |

| 31  | IRQ14                             | 32  | /IOCS16 |  |  |  |  |

| 33  | SA1                               | 34  | NC      |  |  |  |  |

| 35  | SA 0                              | 36  | SA2     |  |  |  |  |

| 37  | /CS0                              | 38  | /CS1    |  |  |  |  |

| 39  | /HDLED                            | 40  | GND     |  |  |  |  |

| 41  | VCC                               | 42  | VCC     |  |  |  |  |

| 43  | GND                               | 44  | NC      |  |  |  |  |

# **13. ETHERNET INTERFACE**

The *MOPS/520* on-board Ethernet interface is based on the Davicom DM9102A PCI Fast Ethernet Controller. This network controller supports a 10/100Base-T interface. The device auto-negotiates whether a 10Mbit/sec or 100Mbit/sec connection is to be used.

All major network operating systems, and several real-time and embedded operating systems support the interface.

The DM9102A provides the following features:

- Integrated Fast Ethernet MAC, Physical Layer and transceiver in one chip

- Compliance with PCI specification 2.2

- PCI bus master architecture

- EEPROM 93C46 interface supports node ID access configuration information

- Compliance with IEEE 802.3u 100Base-TX and 802.3 10Base-T

- Compliance with IEEE 802.3u auto-negotiation protocol for automatic link type selection

- Full Duplex/Half Duplex capability

- Support IEEE 802.3x Full Duplex Flow Control

- Digital clock recovery circuit using advanced digital algorithm to reduce jitter

- High performance 100Mbps clock generator and data recovery circuit

- Provides Loopback mode for easy system diagnostics

## 13.1 Configuration

The on-board PCI Ethernet interface is configured by the BIOS configuration manager. It will be assigned to an available I/O and IRQ location.

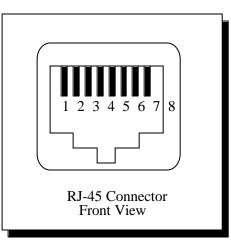

## **13.2 Connectors**

The 10/100Base-T connector is a standard 8-pin RJ45 jack

#### 13.2.1 RJ45 Pinout

| PIN# | SIGNALNAME | FUNCTION              | IN/OUT              |